# PHILIPS

- LOGIC ANALYZERS PM 3580/PM 3585

- **Workshop Service Manual**

FLUKE AND PHILIPS - THE GLOBAL ALLIANCE IN TEST & MEASUREMENT

**PHILIPS**

#### GENERAL.

#### I.1 GENERAL INFORMATION.

This manual contains all the information for completing installation, maintenance, calibration and servicing on the Logic Analyzers in the PM 3580/PM 3585 series.

Great care has been taken to ensure that all the information contained within this manual is complete and accurate. If, however, you find any omissions, or have any suggestions, please send your comments to the address below.

PHILIPS INTERNATIONAL B.V.

INDUSTRIAL ELECTRONICS, T&M DIVISION

SUPPLY CENTRE CUSTOMER SUPPORT DEPARTMENT

BUILDING TQ III - 4

5600 MD EINDHOVEN

THE NETHERLANDS

TELEX: NLFEVSI

JTN

This Philips guarantee is in addition to all rights which the buyer may have against his supplier under the sales agreement between the buyer and the supplier and according to local legislation.

Philips guarantees this product to be free from defects in material and workmanship under normal use and service for a period of one (1) year from the date of shipment. This guarantee does not cover possible required re-calibration and/or standard maintenance actions. This guarantee extends only to the original purchaser and does not apply to fuses batteries or to any product or part thereof that has been misused, altered or has been subjected to abnormal conditions of operation and handling.

Fluke/Philips- supplied software is guaranteed to be properly recorded on non-defective media. We will replace improperly recorded media without charge for 90 days after shipment upon receipt of the software. Our software is not guaranteed to be error free.

Philips obligation under this guarantee is limited to have repaired or replace a product that is returned to an authorised Philips Service Centre within the guarantee period, provided that Philips determines that the product is defective and that the failure has not been caused by misuse, alteration or abnormal operation.

Guarantee service for products installed by Philips will be performed at the Buyer's facility at no charge within Philips' service travel area; outside this area guarantee service will be performed at the Buyer's facility only upon Philips' prior agreement and the Buyer shall pay Philips round trip travel expenses.

If a failure occurs, send the product, freight prepaid to the Service Centre designated by Philips with a description of the difficulty. At Philips option, repairs will be made or the product will be replaced. Philips shall return the product, F.O.B. Repair Centre, transportation prepaid, unless the product is to be returned to another country, in which case the Buyer shall pay all shipping charges, duties and taxes. Philips assumes NO risk for damage in transit.

#### Disclaimer

The foregoing guarantee is exclusive and is in lieu of all other guarantees, expressed or implied, including but not limited to any implied guarantee of merchantability, fitness, adequacy for any particular purpose or use. We shall not be liable for any direct, indirect, special, incidental, or consequential damages, whether based on contract, tort, or otherwise. Some countries or states do not allow the foregoing limitations. Other rights may also vary.

#### SAFETY INSTRUCTIONS.

Read these pages carefully before installation and use of the instrument.

#### INTRODUCTION

The following clauses contain information, cautions and warnings which must be followed to ensure safe operation and to retain the instrument in a safe condition.

Adjustment, maintenance and repair of the instrument must only be carried out by qualified personnel.

#### SAFETY PRECAUTIONS

For the correct and safe use of this instrument it is essential that both operating and service personnel follow generally-accepted safety procedures in addition to the safety precautions specified in this manual.

Specific warning and caution statements, where they apply, will be found throughout the manual. Where necessary, the warning and caution statements and/or symbols are marked on the apparatus.

#### CAUTION AND WARNING STATEMENTS

CAUTION: IS USED TO INDICATE THE CORRECT OPERATION AND MAINTENANCE

PROCEDURES IN ORDER TO PREVENT DAMAGE TO OR DESTRUCTION OF

THE EQUIPMENT OR OTHER PROPERTY.

WARNING: CALLS ATTENTION TO A POTENTIAL DANGER THAT REQUIRES CORRECT

PROCEDURES OR PRACTICES IN ORDER TO PREVENT PERSONAL INJURY.

#### SYMBOLS

High Voltage (red) ≥ 1000V

Live Part (black/yellow)

Read the operating instructions

Protective earth (grounding) terminal

Whenever it is likely that safety-protection has been impaired, the instrument must be made inoperative and be secured against unintentional operation. The matter should then be referred to qualified technicians.

Safety protection is likely to be impaired if, for example, the instrument fails to perform the intended measurements or shows visible damage.

1.5 GENERAL CLAUSES.

WARNING:

THE OPENING OF COVERS OR THE REMOVAL OF PARTS, EXCEPT THOSE TO WHICH ACCESS CAN BE GAINED BY HAND, IS LIKELY TO EXPOSE LIVE PARTS AND ACCESSIBLE TERMINALS WHICH CAN BE DANGEROUS TO LIFE.

- The instrument must be disconnected from all voltage sources before it is opened.

- Note that capacitors inside the instrument can hold their charge even if the instrument has been disconnected from all voltage sources.

- Components that are important for the safety of the instrument may only be renewed by components obtained through your local Philips organisation.

- After repair and maintenance in the primary circuit safety inspection and tests must be carried out.

- All of the screws that are used to fix the system board to the frame of the logic analyzer must be in place at the completion of servicing as they have an effect on the EMC of the instrument.

- Before any connection to the input connectors is made, the instrument must be connected to a protective earth conductor via the three-core mains cable; the mains plug must only be connected to a socket outlet provided with a protective earth contact. The protective action must not be negated by the use of an extension cord without protective conductor.

WARNING:

ANY INTERRUPTION OF THE PROTECTION EARTH CONNECTOR INSIDE OR OUTSIDE THE INSTRUMENT OR THE DISCONNECTION OF THE PROTECTION EARTH TERMINAL IS LIKELY TO MAKE THE INSTRUMENT DANGEROUS. INTENTIONAL INTERRUPTION IS PROHIBITED.

BEFORE CONNECTING THE EQUIPMENT TO THE MAINS OF THE BUILDING INSTALLATION, THE PROPER FUNCTIONING OF THE PROTECTIVE EARTH LEAD OF THE BUILDING INSTALLATION NEEDS TO BE VERIFIED.

## LIST OF CHAPTERS.

| I. | GENE | AL                                                      | į   |

|----|------|---------------------------------------------------------|-----|

|    | 1.1  | GENERAL INFORMATION                                     | i   |

|    | 1.2  | GUARANTEE STATEMENT                                     | ii  |

|    | 1.3  | SAFETY INSTRUCTIONS                                     | III |

|    | 1.4  | IMPAIRED SAFETY PROTECTION                              | IV  |

|    | 1.5  | GENERAL CLAUSES                                         | ίV  |

|    | **** |                                                         |     |

| 1. | INTR | DUGITON                                                 | 1   |

|    | 1.1  | SYSTEM CONFIGURATION                                    | 2   |

|    | 1.2  | PERIPHERAL EQUIPMENT                                    | 3   |

| _  | INCT | LATION AND DISMANTLING                                  | 1   |

| 2. | 2.1  | GENERAL INFORMATION                                     | 2   |

|    | 2.1  | 2.1.1 SAFETY NOTICE                                     | 2   |

|    |      | 2.1.2 REQUIRED TOOLS AND MATERIALS                      | 3   |

|    |      | MAINS VOLTAGE SETTING                                   | 4   |

|    | 2.2  | ACCESS TO PARTS                                         | 5   |

|    | 2.3  | - 5.7.7.7.7.7.7.7.7.1.1.1.1.1.1.1.1.1.1.1.              | 5   |

|    |      |                                                         | 6   |

|    |      |                                                         | 7   |

|    |      | 2.3.3 HANDLE                                            | 8   |

|    |      | 2.3.4 DISK DRIVE ASSEMBLY                               | 9   |

|    |      | 2.3.5 KEYBOARD ASSEMBLY                                 | 10  |

|    |      |                                                         |     |

|    |      | 2.5.7 TOWER COLLEGE COLLEGE                             | 11  |

|    |      | 2.0.0 TAN ONLY ACCEMBET                                 | 12  |

|    |      | 2.3.9 VISUAL DISPLAY UNIT ASSEMBLY                      | 13  |

| 3. | MAIN | RAME                                                    | 1   |

| ٥. | 3.1  | GENERAL INTRODUCTION                                    | 2   |

|    | 3.2  | POWER SUPPLY                                            | 3   |

|    | 3.2  | 3.2.1 Block Diagram description                         | 4   |

|    |      | 3.2.2 Circuit description                               | 7   |

|    | 3.3  | FLOPPY DISK DRIVE                                       | 13  |

|    | 3.3  | 3.3.1 Drive Performance Specifications                  | 13  |

|    |      | 3.3.2 Drive Reliability                                 | 13  |

|    |      | 3.3.3 Electronic Circuitry                              | 13  |

|    |      | 3.3.4 Setting the jumpers on a replacement floppy drive | 15  |

|    |      | KEYBOARD                                                | 18  |

|    | 3.4  |                                                         | 21  |

|    | 3.5  | VIDEO MONITOR                                           |     |

|    |      |                                                         | 21  |

|    |      | 3.5.2 Circuit description                               | 21  |

|    | 3.6  | FAN UNIT                                                | 25  |

|    | 3.7  | MAIN-BOARD HARDWARE DESCRIPTION                         | 25  |

|    |      | 3.7.1 General structure main-board                      | 25  |

|    |      | 3.7.2 The different boards                              | 26  |

|    |      | 3.7.3 The CPU section                                   | 29  |

|    |      | 3.7.4 Data Acquisition section                          | 48  |

| 4. | 4.1<br>4.2 | 4.2.2 POWER S   | MATION         | ENT<br>G<br>NITOR | OCK     | <br> |      |       | 3 3 6 |

|----|------------|-----------------|----------------|-------------------|---------|------|------|-------|-------|

|    | 4.3        |                 | SETTINGS       |                   |         |      |      |       | 13    |

| 5. | ADAP       | TORS            | ******         |                   |         | <br> | <br> |       | . 1   |

|    | 5.1        | INTRODUCTION .  |                |                   |         |      |      |       |       |

|    |            | 5.1.1 TIMING A  | DAPTORS        |                   |         | <br> | <br> |       | . 2   |

|    |            |                 | OCESSOR ADAPT  |                   |         |      |      |       |       |

|    |            |                 | SIGNAL PATH .  |                   |         |      |      |       |       |

|    | 5.2.       | SERVICING THE   | ADAPTORS       |                   |         | <br> | <br> |       | . 4   |

|    | 5.3.       | CURRENTLY SUP   | PORTED ADAPTO  | DRS               | • • • • | <br> | <br> | • • • | . 6   |

| 6. |            | DIAGNOSTIC TES  |                |                   |         |      |      |       |       |

|    | 6.1        | GENERAL INFOR   | MATION         |                   |         | <br> | <br> |       | . 2   |

|    |            | 6.1.1 TEST EQU  | JIPMENT        |                   |         | <br> | <br> |       | . 3   |

|    | 6.2        | POWER ON SELF   | TEST           |                   |         | <br> | <br> |       | . 3   |

|    |            | 6.2.1 GENERAL   |                |                   |         | <br> | <br> |       |       |

|    |            | 6.2.2 STACK TE  | ST             |                   |         | <br> | <br> |       | . 3   |

|    |            | 6.2.3 ROM TEST  | т              |                   |         | <br> | <br> |       |       |

|    |            | 6.2.4 RAM TEST  | Г              |                   |         | <br> | <br> |       |       |

|    |            | 6.2.5 FLOPPY C  | CONTROLLER TES | ST                |         | <br> | <br> |       | . 4   |

|    |            | 6.2.6 MULTI FU  | NCTION PERIPHE | ERAL (MFP         | )       | <br> | <br> |       | . 4   |

|    | 6.3        | DIAGNOSTIC TES  | T DISKETTE     |                   |         | <br> | <br> |       | . 4   |

|    |            |                 | Г              |                   |         |      |      |       |       |

|    |            |                 |                |                   |         |      |      |       |       |

|    |            |                 | NTROLLER TEST  |                   |         |      |      |       |       |

|    |            | 6.3.4 68070 TIM | IER TEST       |                   |         | <br> | <br> |       | . 9   |

|    |            | 6.3.5 KEYBOAR   | D TEST         |                   |         | <br> | <br> |       | . 9   |

|    |            | 6.3.6 RS-232 C  | ONNECTOR       |                   |         | <br> | <br> |       | 10    |

|    |            | 6.3.7 CENTRON   | IICS TEST      |                   |         | <br> | <br> |       | 10    |

|    |            |                 | CONTROLLER     |                   |         |      |      |       | 12    |

|    |            | 6.3.9 SET DATE  | AND TIME       |                   |         | <br> | <br> |       | 13    |

|    |            |                 | NCTION PERIPHE |                   |         |      |      |       | 13    |

|    |            |                 | RGET           |                   | •       |      |      |       | 13    |

|    | 6.4        | BOUNDARY SCAL   |                |                   |         |      |      |       | 14    |

|    | 0.4        |                 | INFORMATION .  |                   |         |      |      |       | 14    |

|    |            |                 | EPORTS         |                   |         |      |      |       | 19    |

|    |            |                 |                |                   |         |      |      |       | 20    |

|    |            |                 | TIONS OF ERROR |                   |         |      |      |       | 21    |

|    |            |                 |                |                   |         | <br> | <br> |       |       |

| 7. |             | CORRECTIVE MAINTENANCE                    | 1  |

|----|-------------|-------------------------------------------|----|

| •  | 7.1         | REPLACEMENTS                              | 2  |

|    |             | 7.1.1 STANDARD PARTS                      | 2  |

|    |             | 7.1.2 SPECIAL PARTS                       | 2  |

|    |             | 7.1.3 TRANSISTORS AND INTEGRATED CIRCUITS | 2  |

|    |             | 7.1.4 STATIC SENSITIVE COMPONENTS         | 3  |

|    | 7.2         | SOLDERING TECHNIQUES                      | 4  |

|    | 17. (17.44) | 7.2.1 SEMICONDUCTORS                      | 4  |

|    |             | 7.2.2 MICRO-MINIATURE SEMICONDUCTORS      | 5  |

|    |             | 7.2.3 ASIC's                              | 5  |

|    | 7.3         | RE-CALIBRATION AFTER REPAIR               | 9  |

|    |             |                                           | 4  |

| 8. | SPEC        | FICATION                                  | 1  |

|    | 8.1         | GENERAL CHARACTERISTICS                   | 3  |

|    |             | 8.1.1 DIMENSIONS                          | 3  |

|    |             | 8.1.2. WEIGHT                             | 3  |

|    |             | 8.1.3 DISPLAY                             | 3  |

|    |             | 8.1.4. POWER                              | 3  |

|    | 8.2         | ENVIRONMENTAL DATA                        | 3  |

|    |             | 8.2.1 STANDARDS                           | 3  |

|    |             | 8.2.2 TEMPERATURE                         | 3  |

|    |             | 8.2.3 RELATIVE HUMIDITY                   | 3  |

|    |             | 8.2.4 ALTITUDE                            | 4  |

|    |             | 8.2.5 VIBRATION                           | 4  |

|    |             | 8.2.6 EMI                                 | 4  |

|    |             | 8.2.7 SAFETY                              | 4  |

|    | 8.3         | INPUT SECTION                             | 4  |

|    | 8.4         | CONFIGURATIONS                            | 5  |

|    |             | 8.4.1 TIMING ANALYZER                     | 5  |

|    |             | 8.4.2 GLITCH ANALYZER                     | 5  |

|    |             | 8.4.3 STATE ANALYZER                      | 6  |

|    | 8.5         | DATA MEMORY STORAGE MODES                 | 7  |

|    | 8.6         | TRIGGER SEQUENCER                         | 8  |

|    |             | 8.6.1 TRIGGER RECOGNIZER'S                | 9  |

|    |             | 8.6.2 TIME-OUT COUNTER                    | 10 |

|    |             | 8.6.3 TRIGGER POSITIONS                   | 10 |

|    |             | 8.6.4 EXTERNAL TRIGGERING                 | 10 |

|    |             | 8.6.5 SELECTIVE STATE STORAGE             | 11 |

|    | 8.7         | ACQUISITION FUNCTIONS                     | 11 |

|    | 8.8         | LOGIC PROBING                             | 12 |

|    | 8.9         | LABEL FORMATTING AND ATTRIBUTES           | 12 |

|    | 8.10        | DATA DISPLAY                              | 12 |

|    | 8.11        | DATA/SETTING STORAGE                      | 13 |

|    | 8.12        | HARD-COPY OUTPUT                          | 13 |

|    | 8.13        | EXTERNAL VIDEO OUTPUT                     | 14 |

|    | 8.14        | EXTERNAL BNC TRIGGER                      | 14 |

|    | 8.15        | EXTERNAL BNC TRIGGER OUT                  | 14 |

|    |             |                                           | _  |

| 9.    | SPARE | PART  | rs .  |       |         |          |     |     |    |       |   |   | • |      |    |   |   |  |     |   |       |   | . 60 | 1   |

|-------|-------|-------|-------|-------|---------|----------|-----|-----|----|-------|---|---|---|------|----|---|---|--|-----|---|-------|---|------|-----|

|       | 9.1   | UNITS | 5 &   | ASSE  | MBL     | IES      |     |     |    |       |   |   |   |      |    |   |   |  |     |   |       |   |      | 2   |

|       | 9.2   | MAIN  | BO    | ARD F | PART    | TS .     |     |     |    |       |   |   |   | <br> |    |   |   |  | •   |   | <br>• |   |      | 3   |

|       |       | 9.2.1 | AS    | SIC's |         |          |     |     |    |       |   |   |   |      | ٠. |   | ٠ |  |     |   |       |   | ( 16 | 3   |

|       |       | 9.2.2 | IN    | TEGR  | ATE     | DC       | IRC | UI  | rs |       |   |   |   |      |    |   |   |  |     | • | <br>• |   |      | 3   |

|       |       | 9.2.3 | XT    | ALS   |         |          |     |     |    |       |   |   |   |      |    |   |   |  | 90% | • | <br>* |   |      | 4   |

|       |       | 9.2.4 | SE    | MI-C  | OND     | UC.      | TOF | RS  |    | <br>• |   |   |   |      |    |   | ÷ |  |     | • |       |   |      | 4   |

|       |       | 9.2.5 | C     | APACI | ITOF    | RS .     |     |     |    |       |   |   |   |      |    | • |   |  |     |   |       |   |      | 4   |

|       |       | 9.2.6 | RE    | SIST  | ORS     |          |     |     |    |       |   |   |   |      |    |   |   |  |     |   |       |   |      | 5   |

|       |       | 9.2.7 |       | ONNE  |         |          |     |     |    |       |   |   |   |      |    |   |   |  |     |   |       |   |      |     |

|       |       | 9.2.8 |       | SCEL  |         |          |     |     |    |       |   |   |   |      |    |   |   |  |     |   |       |   |      | 2.0 |

|       | 9.3   | MONI. |       |       |         |          |     |     |    |       |   |   |   |      |    |   |   |  |     |   |       |   |      | 523 |

|       | 0.0   | 9.3.1 |       | ONTR  | 2000000 | T18.5.00 |     | -   |    |       |   |   |   |      |    |   |   |  |     |   |       |   |      |     |

|       |       | 9.3.2 |       | RT BC |         |          |     |     |    |       |   |   |   |      |    |   |   |  |     |   |       |   |      | 22  |

|       | 9.4   | 0.0.2 |       | OWER  |         |          |     |     |    |       |   |   |   |      |    |   |   |  |     |   |       |   |      |     |

|       | 9.5   |       |       | EYBO  |         |          |     |     |    |       |   |   |   |      |    |   |   |  |     |   |       |   |      | 10  |

|       | 9.6   |       | 10000 | ENER  |         |          |     |     |    |       |   |   |   |      |    |   |   |  |     |   |       |   |      | 10  |

|       | 9.7   |       |       | DAPTO |         |          |     | 5.5 | -  |       |   |   |   |      |    |   |   |  |     |   |       |   |      | 11  |

|       | 9.8   |       |       | STE   |         |          |     |     |    |       | - |   |   |      |    |   |   |  |     |   |       |   |      | 11  |

|       | 3.0   |       |       |       | <b></b> |          |     |     |    | •     | • | • | • |      |    |   | - |  |     |   |       | • | •    |     |

| INDEX |       |       |       |       |         |          |     |     |    |       |   |   |   |      |    |   |   |  |     |   |       |   |      | 1   |

|       |       |       |       |       |         |          |     |     |    |       |   |   |   |      |    |   |   |  |     |   |       |   |      |     |

JTN

## LIST OF FIGURES.

|                                                  | 1    |

|--------------------------------------------------|------|

| 2.1. The voltage selector assembly               | . 4  |

| 2.2. The rear plate assembly                     | . 5  |

| 2.3 The sleeve assembly                          | . 0  |

| 2.4 Assembly of the handle                       | . 1  |

| 2.5. Disk drive assembly                         | . 8  |

| 2.6 Keyboard assembly                            | . 9  |

| 2.7 Main board assembly                          | 10   |

| 2.8 Power supply unit assembly                   | 11   |

| 2.9 Fan unit assembly                            | 12   |

| 2.10. VDU assembly                               | 13   |

|                                                  |      |

| 3.1. Block diagram power supply                  | . 5  |

| 3.2. Drawing Primary Circuit                     | 0    |

| 3.3. Diagram control circuit 1                   | 9    |

| 3.4. Diagram control circuit 2                   | . 10 |

| 3.5. Location of the jumper block of the SMD-340 | . 15 |

| 3.6. Location of the jumper block of the SMD-440 | . 16 |

| 3.7. Floppy disk drive interconnections          | . 17 |

| 3.8. Unit drawing keyboard                       | . 18 |

| 3.9. Circuit diagram keyboard                    | . 19 |

| 3.10. Circuit diagram monitor control board      | . 20 |

| 3.11. Circuit diagram CRT board                  | . 23 |

| 3.12. Unit drawing video monitor                 | . 24 |

| 3.13. General structure of Analyzer main-board   |      |

| 3.14. Unit drawing 200 MHz main-board            |      |

| 3.15. Unit drawing 100 MHz main-board            |      |

|                                                  |      |

| 3.16. The CPU section                            |      |

| 3.17. The Static RAM and EPROM                   |      |

| 3.18. The Dynamic RAM (part 1)                   | . 33 |

| 3.19. The Dynamic RAM (part 2)                   | . 34 |

| 3.20. Data bus buffers                           |      |

| 3.21. Address bus buffers                        |      |

| 3.22. Floppy disc controller                     | . 41 |

| 3.23. Centronics parallel controller             |      |

| 3.24. Multi function peripheral                  |      |

| 3.25. GPIB controller                            |      |

| 3.26. Data input                                 | . 51 |

| 3.27. Calibration circuit                        | . 52 |

| 3.28. POD input connector                        | . 53 |

| 3.29. Trigger control circuit                    | . 55 |

|                                                  |      |

| 4.1. Power supply adjustment                     | 4    |

| 4.2. Video display adjustment                    | 7    |

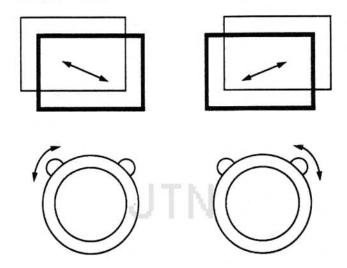

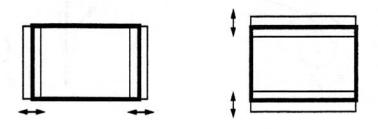

| 4.3. Horizontal alignment                        |      |

| 4.4. Screen centre adjustment                    |      |

| 4.5. Screen width & height correction            |      |

| 4.6. Screen corner corrections                   | 7777 |

| 4.7. Real time clock adjustment                  |      |

| 4.8. The jumpers to be set on the main-board     |      |

| 4.6. The lumbers to be set on the main-board     | . 13 |

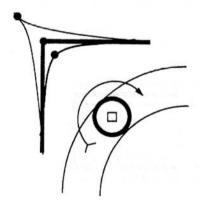

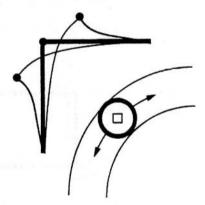

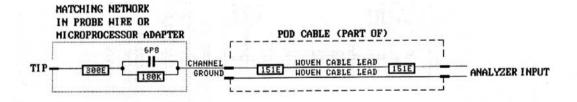

| 51   | Overall signal path                | ¥ C |     |  |  | •00 | <br>• | <br> |   |   |   |     |   |   |        |   |   | <br> |   |   |   |    |   | . з |

|------|------------------------------------|-----|-----|--|--|-----|-------|------|---|---|---|-----|---|---|--------|---|---|------|---|---|---|----|---|-----|

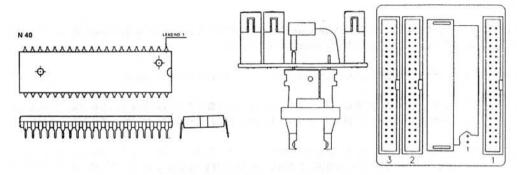

| 5.2  | DIP package and adaptor            |     |     |  |  |     |       | <br> |   |   |   |     |   |   |        |   |   | <br> |   |   |   |    |   | . 4 |

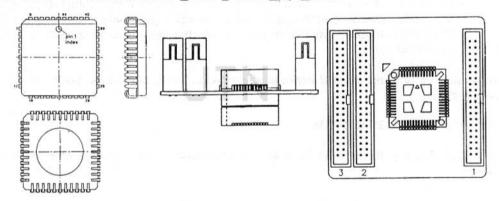

| 5.3. | PLCC package and adaptor           | •   |     |  |  |     |       | <br> |   |   |   |     |   | ٠ |        |   |   | <br> |   |   |   |    |   | . 4 |

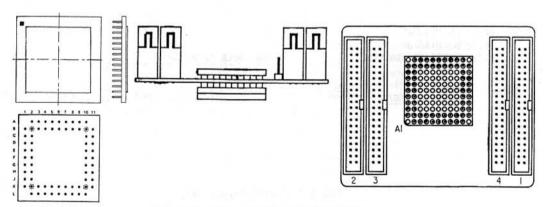

| 5.4. | PGA package and adaptor            | •   |     |  |  |     | <br>٠ | <br> | • | ٠ |   | •   |   |   |        |   | • | <br> | • |   |   |    |   | . 4 |

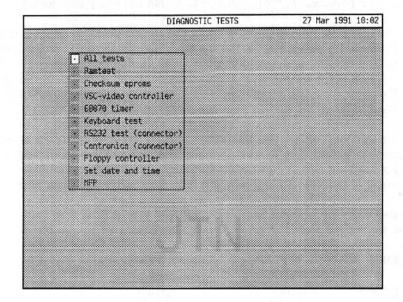

| 6.1. | Test selection menu                |     |     |  |  |     |       |      |   |   |   |     |   |   | <br>   |   |   | <br> | • | × |   |    |   | . 5 |

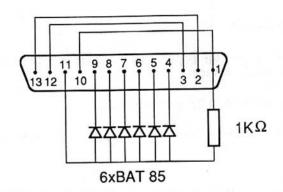

| 6.2. | Centronics diode matrix connector  |     |     |  |  |     |       |      | • | • |   | ٠   |   |   |        |   |   | <br> |   | • | • |    | • | 11  |

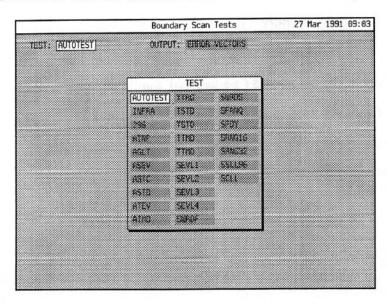

| 6.3. | Boundary Scan test disk 1          |     |     |  |  |     |       |      | • | • |   | •   | • |   | <br>•  | ٠ |   | <br> | ٠ |   |   |    | • | 16  |

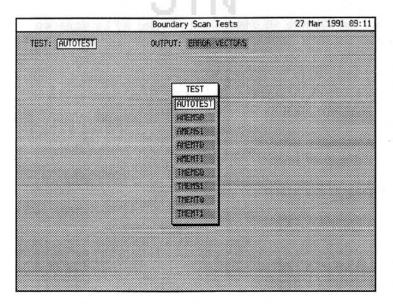

| 6.4. | Boundary Scan Tests disk 2         |     |     |  |  | ×   | <br>٠ |      |   | ٠ |   |     | • |   | <br>٠. |   | ٠ |      | • |   |   | ٠. |   | 16  |

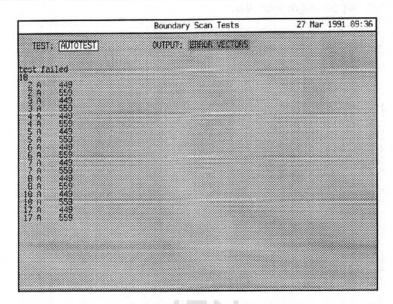

| 6.5. | Error message with VECTORS         |     |     |  |  | ٠   |       |      |   |   |   |     |   |   | <br>   | ٠ |   |      |   |   |   |    | • | 21  |

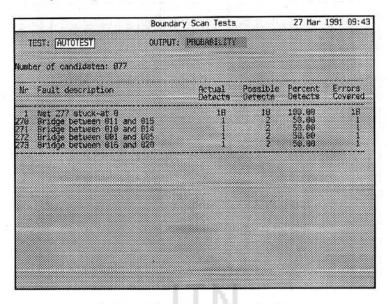

| 6.6. | Error report PROBABILITY           | •   |     |  |  |     |       |      |   |   |   |     |   |   | <br>   |   | • |      | • |   |   |    |   | 22  |

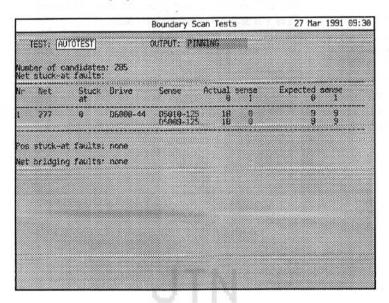

| 6.7. | Stuck at error report with PINNING |     |     |  |  |     |       |      |   |   |   | o o |   |   | <br>   |   |   |      |   |   | • |    |   | 24  |

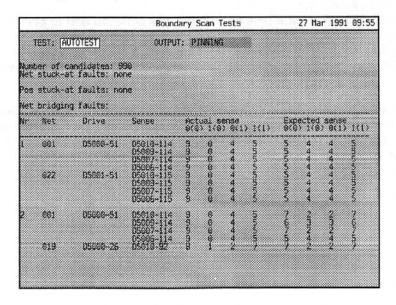

| 6.8. | Bridging error report with PINNING |     |     |  |  |     |       |      |   |   |   |     |   |   | <br>   |   |   |      |   |   |   |    |   | 26  |

| 6.9. | Error report with DIAGNOSTIC       |     | • • |  |  |     | <br>• |      |   | • | • |     |   |   |        | ٠ | • |      |   |   |   |    |   | 28  |

NOTE: Words print

Words printed in {bold; italic} are stated in the Index in the back of this manual.

JTN

# CHAPTER 1.

1. INTRODUCTION.

CONTENTS.

| Section | 1    |                      |  |  |  |      |  |  |  |  |  |  |     |  |  | P | age |

|---------|------|----------------------|--|--|--|------|--|--|--|--|--|--|-----|--|--|---|-----|

| 1.      | INTR | ODUCTION             |  |  |  |      |  |  |  |  |  |  |     |  |  |   |     |

|         | 1.1  | SYSTEM CONFIGURATION |  |  |  | <br> |  |  |  |  |  |  | . , |  |  |   | 2   |

|         | 1.2  | PERIPHERAL EQUIPMENT |  |  |  | <br> |  |  |  |  |  |  |     |  |  |   | 3   |

JTN

#### 1.1 SYSTEM CONFIGURATION.

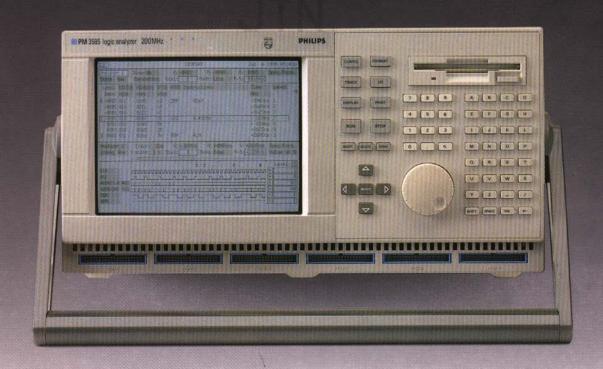

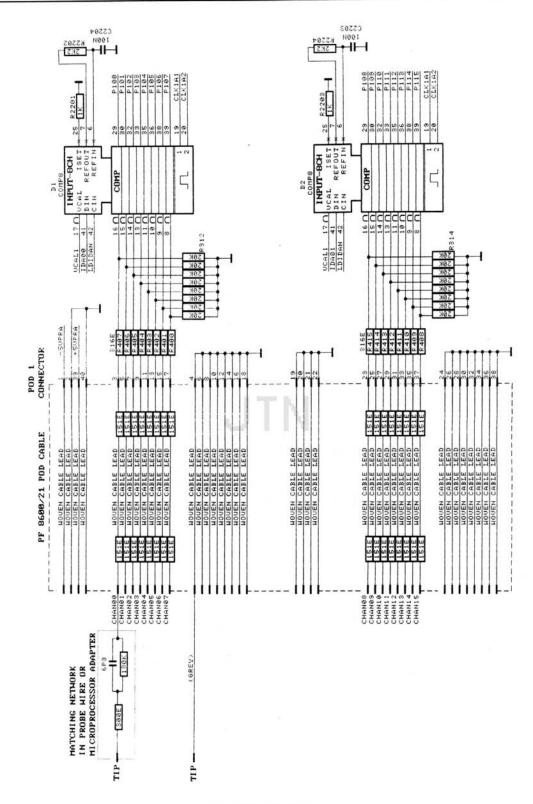

The PM 3580/PM 3585 family of logic analyzers are State and Timing Logic Analyzers for use within the R & D, Manufacturing, Service and Education environments. They are available in 32/64/96 channel models. The operating speed of the PM 3580 is 100 MHz and the operating speed of the PM 3585 is 200 MHz.

The PM 3580 and the PM 3585 each come in two basic models, these are:

- PM 3580/30 32 dual analysis channels with 100 MHz Timing, 50 MHz state and 1K deep acquisition memory.

- PM 3580/60 64 dual analysis channels with 100 MHz Timing, 50 MHz state and 1K deep acquisition memory.

- PM 3585/60 64 dual analysis channels with 200 MHz Timing, 50 MHz state and 2K deep acquisition memory.

- PM 3585/90 96 dual analysis channels with 200 MHz Timing, 50 MHz state and 2K deep acquisition memory.

#### All of the above models have the following standard features:

- Human interface of an integral keypad and rotary knob, and a nine inch white phosphor, high resolution CRT.

- 3.5 inch micro floppy disc drive for setup, storage and retrieval of data.

- Rear mounted BNC connections for input and output of trigger signals.

- External video port.

- Centronics printer interface.

- RS-232-C ports for other peripherals to be connected, e.g. a printer.

- Data acquisition is via any or all of the six inputs on the front of the unit.

The system assembly board centres on the 68070 16/32 bit CPU. It is accompanied by powerful data acquisition ASIC's that analyze the data received from the target system. An interface is used to ensure that the acquisition system is fully compatible with that of the CPU architecture. The system assembly board also contains the circuitry required to interface with the keyboard, disk drive, the CRT and the output ports.

#### PERIPHERAL EQUIPMENT. 1.2

The following accessories are available for the PM 3580 and the PM 3585 series of Logic Analyzers.

| PF 8600/20 | 16 Channel logic pod.                         |

|------------|-----------------------------------------------|

| PF 8600/21 | 16 Channel pod cable for PM 358X.             |

| PF 8600/24 | Gray, low profile, mini measuring clips.      |

| PF 8666/20 | Front cover with integrated acessory pouch.   |

| PF 8669/20 | Logic target.                                 |

| PM 8819/30 | 50 Mini-measuring clips, red/dual pin.        |

| PM 8902/00 | 12V DC/AC converter.                          |

| PM 8902/10 | Mounting kit for PM 8902/00.                  |

| TC 100     | Cart for PM 3580 or PM 3585 with two shelves. |

NOTES.

JTN

# CHAPTER 2.

#### 2. INSTALLATION AND DISMANTLING.

#### CONTENTS.

| Section | า    |          |                           |       |   |    |  |  |      |  |  | 53 |  | Pa | ige |

|---------|------|----------|---------------------------|-------|---|----|--|--|------|--|--|----|--|----|-----|

| 2.      | INST | ALLATION | AND DISMANTLING           |       |   |    |  |  | <br> |  |  |    |  |    | 1   |

|         | 2.1  | GENEF    | RAL INFORMATION           |       |   | ٠. |  |  |      |  |  |    |  |    | 2   |

|         |      | 2.1.1    | SAFETY NOTICE             |       |   |    |  |  | <br> |  |  |    |  |    | 2   |

|         |      | 2.1.2    | REQUIRED TOOLS AND MAT    | ERIAL | S |    |  |  | <br> |  |  | ٠  |  |    | 3   |

|         | 2.2  | MAINS    | <b>VOLTAGE SETTING</b>    |       |   |    |  |  | <br> |  |  |    |  |    | 4   |

|         | 2.3  | ACCES    | S TO PARTS                |       |   |    |  |  | <br> |  |  |    |  |    | 5   |

|         |      | 2.3.1    | REAR ACCESS PLATE         |       |   |    |  |  | <br> |  |  |    |  |    | 5   |

|         |      | 2.3.2    | INSTRUMENT SLEEVE         |       |   |    |  |  | <br> |  |  |    |  |    | 6   |

|         |      | 2.3.3    | HANDLE                    |       |   |    |  |  |      |  |  |    |  |    | 7   |

|         |      | 2.3.4    | DISK DRIVE ASSEMBLY       |       |   |    |  |  |      |  |  |    |  |    | 8   |

|         |      | 2.3.5    | KEYBOARD ASSEMBLY         |       |   |    |  |  |      |  |  | •  |  |    | 9   |

|         |      | 2.3.6    | MAIN BOARD ASSEMBLY       |       |   |    |  |  |      |  |  |    |  |    | 10  |

|         |      | 2.3.7    | POWER SUPPLY UNIT ASSEM   | MBLY  |   |    |  |  |      |  |  |    |  |    | 11  |

|         |      | 2.3.8    | FAN UNIT ASSEMBLY         |       |   |    |  |  |      |  |  |    |  |    | 12  |

|         |      | 2.3.9    | VISUAL DISPLAY UNIT ASSET | MBLY  |   |    |  |  |      |  |  | •  |  |    | 13  |

|         |      |          | 2.3.9.1 Assembly of PCB's |       |   |    |  |  |      |  |  |    |  |    | 13  |

|         |      |          | 2.3.9.2 Assembly of CRT   |       |   |    |  |  |      |  |  |    |  |    | 13  |

#### 2.1 GENERAL INFORMATION.

This section provides the **dismantling procedures** required for the removal of units and components during repair operations. Installation is the reverse procedure of the dismantling described below.

All items removed from the instrument must be adequately protected against damage, and should be put in a safe place. All normal precautions regarding the use of tools must be observed.

During dismantling a careful note must be made of all leads that have to be disconnected so that they can be reconnected to their correct terminals during re-assembly.

#### CAUTION: Damage may result if:

- The instrument is switched on when a unit has been removed or disconnected.

- A unit is removed within one minute of the instrument being switched off.

#### 2.1.1 SAFETY NOTICE.

The opening of covers or the removal of parts, except those to which access can be gained by hand, is likely to expose live parts, note also that accessible terminals may be live.

The instrument must be disconnected from all voltage sources before any adjustment, replacement or maintenance which requires the instrument to be opened.

Any adjustment, maintenance or repair of the instrument that has to be completed while the instrument is under voltage must only be carried out by a skilled person aware of the hazards involved.

The replacement of the mains plug is at the users risk, after a mains plug has been replaced a high voltage test in accordance with IEC publication 348 is strongly recommended.

Ensure that the instrument is set to the local mains voltage before inserting the plug into the mains socket.

Note that capacitors inside the instrument may still be charged even if it has been separated from all voltage sources. Use safety glasses and protective gloves when handling the CRT.

#### 2.1.2 REQUIRED TOOLS AND MATERIALS.

For the complete disassembly of the instrument the following tools are required:

Torx screwdrivers

| SIZE |   | Concern Service code number |

|------|---|-----------------------------|

| T8   |   | 4822 395 50263              |

| T10  | - | 5322 395 50381              |

| T20  | - | 5322 395 50418              |

Flat blade screwdriver (small)

If the nylon tie wraps have been cut away from the internal wiring it is recommended that the wiring is fixed with new ties, service ordering code 5322 401 14154 (per item).

In order to avoid the loss of screws, nuts etc it is good practice to replace them in their original location, if possible, whilst the units are laying apart.

#### 2.2 MAINS VOLTAGE SETTING.

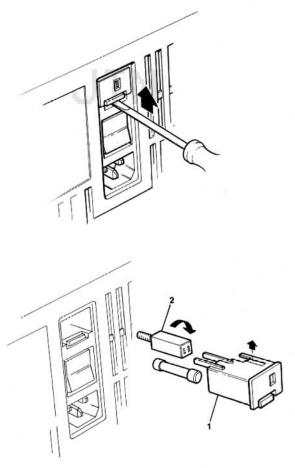

The mains voltage of the instrument is set in the factory and is customised to the requirements of the country of destination. This setting can be changed using the following procedure, the two available settings being those of 110V and 220V.

- Disconnect the mains supply from the Instrument.

- Prise the voltage selector unit (1) from the rear of the instrument.

- Lift the retaining lug that holds the voltage selector (2) into the unit and then remove the selector.

- Rotate the voltage selector so that the required figure will be displayed in the window of the unit and then replace the complete unit in the reverse order of that of the removal procedure.

NOTE:

The correct fuse should be used for each of the voltage settings. The recommended fuse sizes are 2A slow for the 220V setting and 4A slow for the 110V setting.

Fig. 2.1. The voltage selector assembly.

#### 2.3 ACCESS TO PARTS.

Before commencing the removal of any cover or module of this instrument ensure that it has been disconnected from the main voltage supply. Remove any other external connections to the instrument.

#### 2.3.1 REAR ACCESS PLATE.

- Ensure that all external connections to the instrument have been removed.

- Remove the brightness control knob (1) located in the bottom right corner of the rear plate by pulling it away from the spindle.

- Locate and loosen the two Torx screws (2) and washers on the rear cover.

- Remove the rear plate from the unit.

Fig. 2.2. The rear plate assembly.

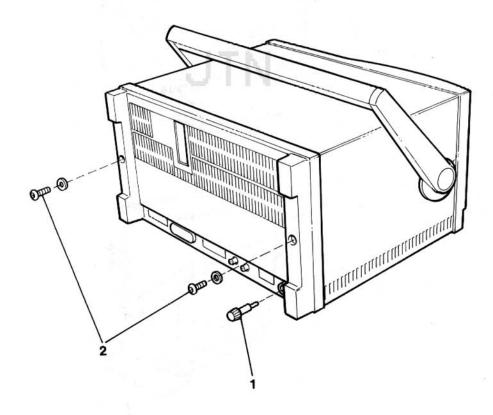

#### 2.3.2 INSTRUMENT SLEEVE.

- Complete procedure 2.3.1.

- Adjust the position of the carrying handle so that it is not obscuring the front of the instrument. (The position of the handle is altered by applying pressure to the centre of handle pivots and then moving the handle.)

- Position the instrument face down on the work surface using a piece of foam rubber (1), or similar material, to prevent the keyboard dial from touching the surface.

- Slide the sleeve (2) of the instrument away from the chassis.

Fig. 2.3. The sleeve assembly.

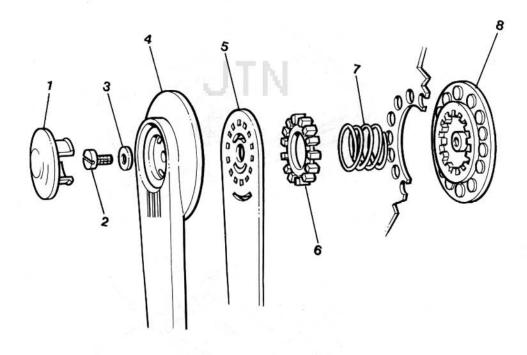

#### 2.3.3 HANDLE.

- Complete procedure 2.3.2.

- Insert a small blade into the slot in the central cover (1) of the handle pivot and prise off, this will reveal a slotted screw (2). Repeat this procedure for the other side of the handle.

- Remove the slotted screws (2) and washers (3) located on either side of the handle that fasten the handle to the instrument sleeve.

- Remove the handle assembly parts (4-8). It is suggested that you reassemble all the component parts of the handle pivot assembly to avoid misplacing them.

NOTE:

Item 6 (stop disk) can be ordered separately at Concern Service. Code 5322 466 92997.

Item 4 (Handle side cover) can be ordered separately at Concern Service. Code 5322 600 30047.

Fig. 2.4. Assembly of the handle.

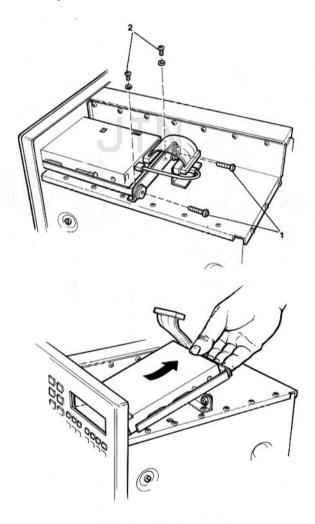

#### 2.3.4 DISK DRIVE ASSEMBLY.

- Complete procedure 2.3.2.

- Disconnect the power cable and ribbon cable attached to the rear of the disk drive.

- Remove the two screws (1) that fasten the disk drive, via grommets located in the bracket, to the cover of the power supply unit,

- If the bracket also has to be removed, remove the two screws (2) that fasten it to the power supply unit cover.

- Remove the disk drive by carefully lifting the rear of the drive so that it is able to clear the bracket and PCB and then gently pull it out of the instrument.

- Remove the disk drive from the mounting bracket by removing the four screws on the underside of the assembly.

Fig. 2.5. Disk drive assembly.

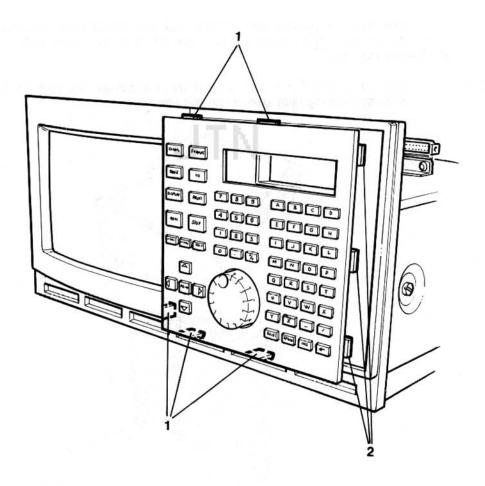

#### 2.3.5 KEYBOARD ASSEMBLY.

- Complete procedure 2.3.4.

- Gently press the fixing lugs (1) that attach the keyboard to the main fascia of the instrument so as to enable it to move.

- Pull the left hand edge of the keyboard toward you and withdraw the pad in the direction of the VDU screen, so as to free the three locating lugs (2).

- Disconnect the four wired plug that is attached to the keyboard.

Fig. 2.6. Keyboard assembly.

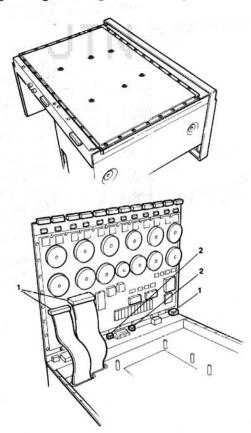

#### 2.3.6 MAIN BOARD ASSEMBLY.

- Complete procedure 2.3.2.

- Position the instrument so that it is upside down with the rear towards you.

- Remove the Torx screws that fasten the metal base plate to the printed circuit board. This

will reveal the underside of the printed circuit board.

# CAUTION When re-assembling the instrument all of the Torx screws that have just been removed must be replaced. Failure to do so will severely affect the operation of the instrument.

- Remove the Torx screws that fasten the rear metal bracket to the main chassis of the instrument.

- Lift the board towards you and gently pull it away from the chassis. Disconnect the three ribbon (1) and two power supply connectors (2) from the board and then continue withdrawing the board.

NOTE: There are twelve IC's located at the front of this board and care must be taken to avoid them being damaged during the removal procedure.

Fig. 2.7. Main board assembly.

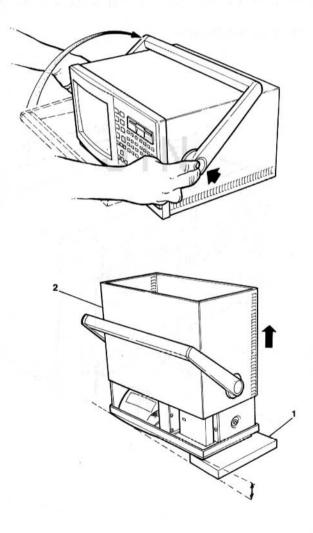

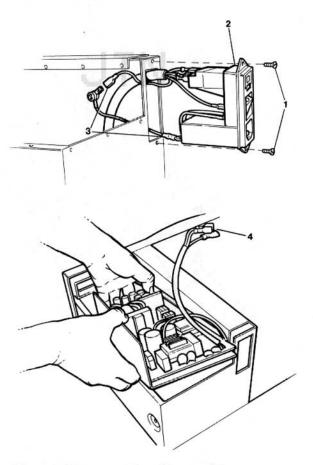

#### 2.3.7 POWER SUPPLY UNIT ASSEMBLY.

- Complete procedure 2.3.4.

- Remove all the Torx screws that fasten the PSU cover to the main chassis of the equipment.

- Disconnect the ribbon cable from the PSU cover.

- Remove the two screws (1) that fasten the mains input socket (2) to the chassis.

- Disconnect the two grounding wires (3) from their respective connectors on the mains input socket and the chassis.

- Disconnect the four wires (4) to the mains input socket, noting their positions and colours for correct reconnection.

- Lift the rear of the PSU circuit board up slightly and then remove the board from the chassis.

- Disconnect the ribbon cable from the front of the PSU.

Fig. 2.8. Power supply unit assembly.

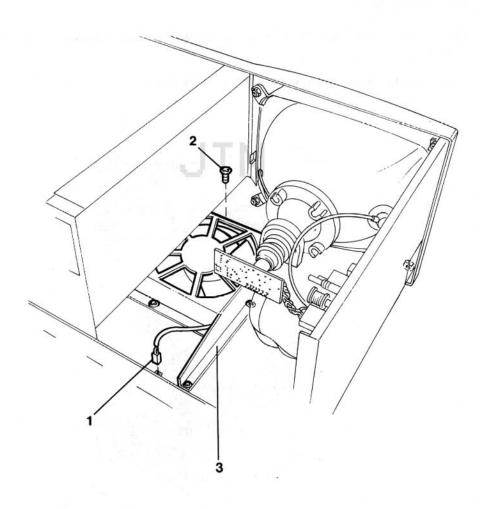

#### 2.3.8 FAN UNIT ASSEMBLY.

- Complete procedure 2.3.2.

- Disconnect the fan unit power supply cable (1) from the socket on the chassis.

- Remove the Torx screws (2) that fasten the fan unit (3) to the instrument chassis.

- Lift the fan unit out of the instrument chassis.

WARNING: TAKE CARE NOT TO DAMAGE THE REAR OF THE CRT SO AS TO AVOID ANY RISK OF IMPLOSION.

Fig. 2.9. Fan unit assembly.

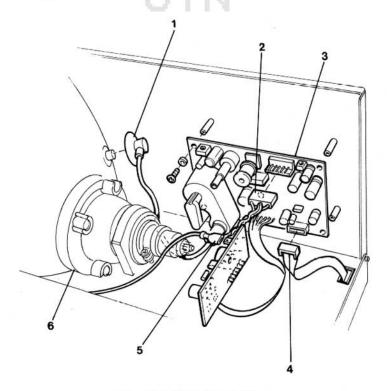

#### 2.3.9 VISUAL DISPLAY UNIT ASSEMBLY.

WARNING: BEFORE COMMENCING ANY TASK ON THE VDU ENSURE THAT THE CRT AND THE EHT CABLE HAVE BEEN DISCHARGED.

#### 2.3.9.1 Assembly of PCB's

- Disconnect the two cables (2, 4) from the PCB and the EHT lead (1) from the CRT.

- Remove the grounding wire (5) from the CRT PCB and then pull this PCB away from the tube.

- Remove the five screws that fasten the PCB (3) to the chassis.

- Place the boards to one side.

#### 2.3.9.2 Assembly of CRT

- Remove the CRT PCB and EHT lead (1).

- Undo the four locknuts that fix the CRT mounting bracket to the chassis of the instrument, being sure to support the CRT at all times. Note that one of the screws is slightly obscured by the fan unit, you may find it easier to complete procedure 2.3.8 before removing the CRT.

- Place the CRT (6) on a scratch free surface.

Fig. 2.10. VDU assembly.

NOTES.

JTN

# CHAPTER 3.

#### 3. MAINFRAME.

#### CONTENTS

| Section |       |        | Pa                                                | age |

|---------|-------|--------|---------------------------------------------------|-----|

| 3.      | MAINF | RAME . |                                                   | 1   |

|         | 3.1   |        | RAL INTRODUCTION                                  | 2   |

|         | 3.2   |        | R SUPPLY                                          | 3   |

| 8       | J     | 3.2.1  | Block Diagram description                         | 4   |

|         |       | 3.2.2  | Circuit description                               | 7   |

|         |       | 0.2.2  | 3.2.2.1 The primary circuit                       | 7   |

|         |       |        | 3.2.2.2 The control circuit 1                     | 8   |

|         |       |        | 3.2.2.3 The control circuit 2                     | 11  |

| 8       | 3.3   | FLOPE  | Y DISK DRIVE                                      | 13  |

|         | 0.0   | 3.3.1  | Drive Performance Specifications                  | 13  |

|         |       | 3.3.2  | Drive Reliability                                 | 13  |

|         |       | 3.3.3  | Electronic Circuitry                              | 13  |

|         |       |        | 3.3.3.1 Drive Connectors                          | 14  |

|         |       | 3.3.4  | Setting the jumpers on a replacement floppy drive | 15  |

|         |       |        | 3.3.4.1 SMD-340 Jumper settings                   | 15  |

|         |       |        | 3.3.4.2 SMD-440 Jumper settings                   | 16  |

|         | 3.4   | KEYBO  | DARD                                              | 18  |

|         | 3.5   |        | MONITOR                                           | 21  |

|         |       | 3.5.1  | General information                               | 21  |

|         |       | 3.5.2  | Circuit description                               | 21  |

|         | 3.6   | FAN U  |                                                   | 25  |

|         | 3.7   | MAIN-  | BOARD HARDWARE DESCRIPTION                        | 25  |

|         |       | 3.7.1  | General structure main-board                      | 25  |

|         |       | 3.7.2  | The different boards                              | 26  |

|         |       | 3.7.3  | The CPU section                                   | 29  |

|         |       |        | 3.7.3.1 The RS232 port                            | 30  |

|         |       |        | 3.7.3.2 The Static RAM                            | 35  |

|         |       |        | 3.7.3.3 The EPROM's                               | 35  |

|         |       |        | 3.7.3.4 The Dynamic RAM's                         | 35  |

|         |       |        | 3.7.3.5 Data buffers                              | 36  |

|         |       |        | 3.7.3.6 Address bus buffers                       | 36  |

|         |       |        | 3.7.3.7 Peripherals                               | 39  |

|         |       | 3.7.4  | Data Acquisition section                          | 48  |

|         |       |        | 3.7.4.1 General                                   | 48  |

|         |       |        | 3.7.4.2 Data input                                | 50  |

|         |       |        | 3.7.4.3 POD Power Supply                          | 53  |

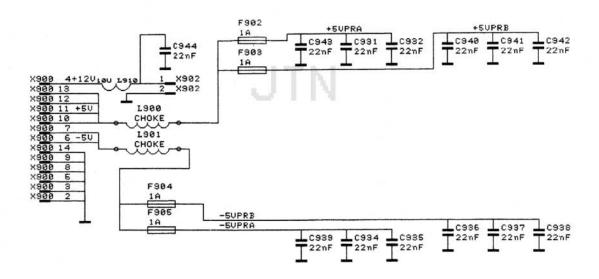

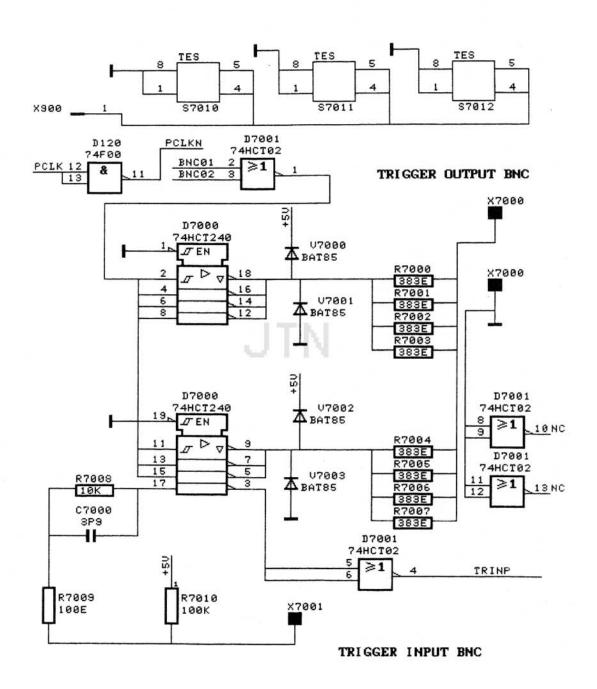

|         |       |        | 3.7.4.4 External Trigger Control                  | 54  |

|         |       |        | 3.7.4.5 Main-board Temperature Guarding           | 54  |

#### 3.1 GENERAL INTRODUCTION.

The mainframe of the Logic Analyzer comprises:

- Power Supply

- Floppy Disk Drive

- Keyboard

- Video Monitor

- Fan Unit

- Main Board

Each of these units will be described in this section.

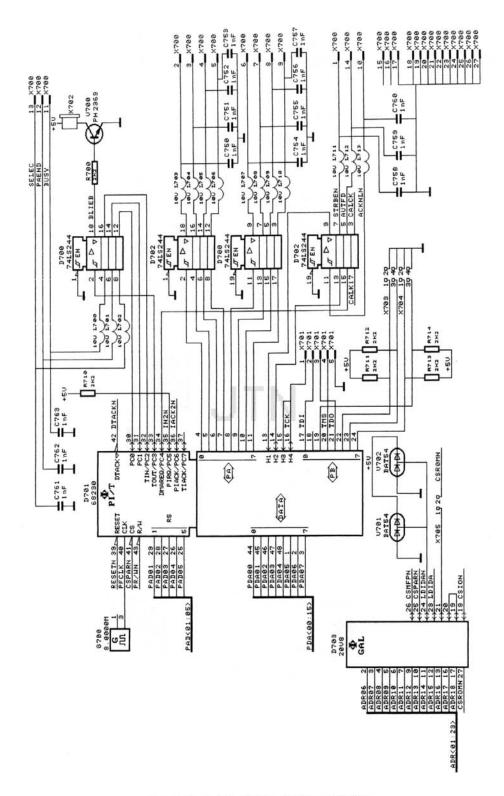

#### 3.2 POWER SUPPLY.

The switch mode power supply in the Analyzer supplies 3 output voltages i.e.

- + 5V / 20A

- +12V / 2A

- 5V / 3A

#### Usage of the D.C. supplies:

- + 5V: by main-board, keyboard and floppy drive.

- +12V: by monitor and fan unit

- 5V : by main-board

The power supply unit has several protection features:

- The mains fuse for over-current protection in the primary stage (2A slow type for 220V and 4A slow type for 110V).

- 2) An over-current sense for the +5V.

- 3) Over-voltage protection's on -5V and +5V.

- Over-current protection for +12V and -5V.

- 5) Thermal sense on heatsinks and externally controllable shutdown input.

If by accident a short circuit is made internally or at the POD input connectors (+5V or -5V shorted to ground), then the Analyzer should be switched off for at least 30 seconds. All output voltages of the power supply will again be available at the next switch on.

#### CAUTION:

ALWAYS USE A SEPARATION TRANSFORMER DURING MEASUREMENTS ON THE POWER SUPPLY. THIS IS NOT ONLY MUCH SAFER BUT ALSO PREVENTS EARTHED TOOLS OR EQUIPMENT FROM BEING SHORTED TO LIVE VOLTAGES.

#### NOTE:

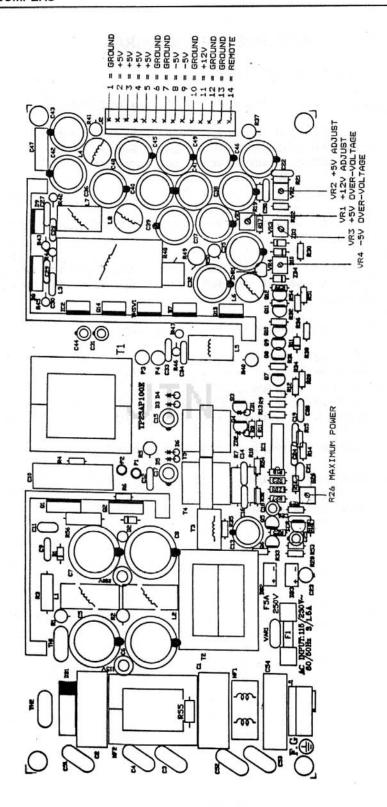

For an Unit Drawing of the power supply refer to Fig. 4.1. of Chapter 4.

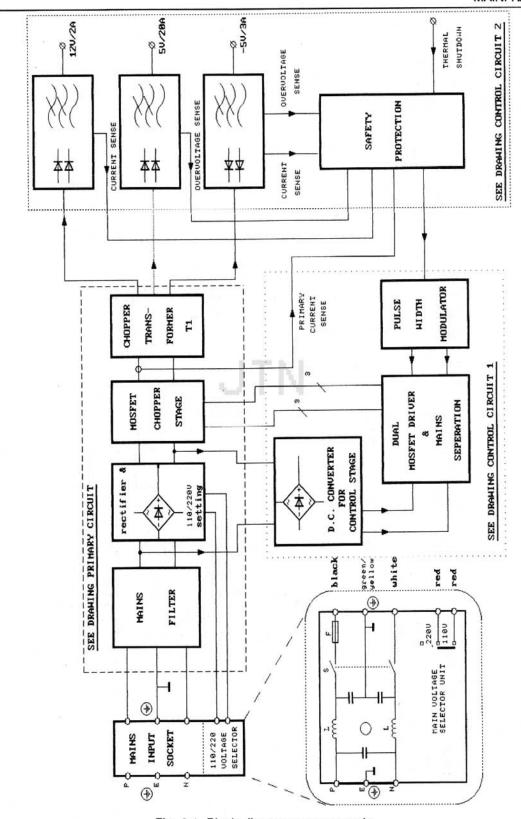

#### 3.2.1 Block Diagram description.

The power supply is of the switched mode type.

The primary rectified mains voltage is chopped by the chopper transistors according to the power desired in the secondary circuit.

The chopper transformer transports the necessary amount of energy to the secondary circuit. The chopper transistors are controlled by the pulse width modulator (PWM) circuitry. This PWM will increase the pulse width as soon as the load in the secondary circuit increases and vice versa. In this way the output voltages are stabilized.

As soon as an emergency situation is sensed (short circuit, over voltage, over-current or overheating) the safety protection circuit will immediately shut down the PWM and by this the chopper stage.

Thus the output voltage's of the secondary circuit are switched off.

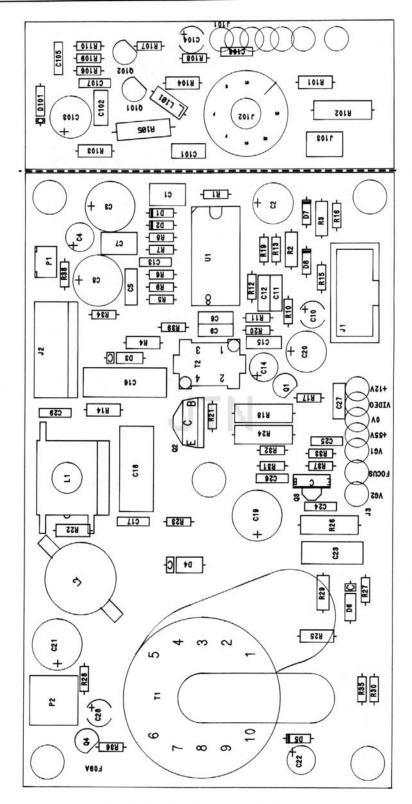

Fig. 3.1. Block diagram power supply.

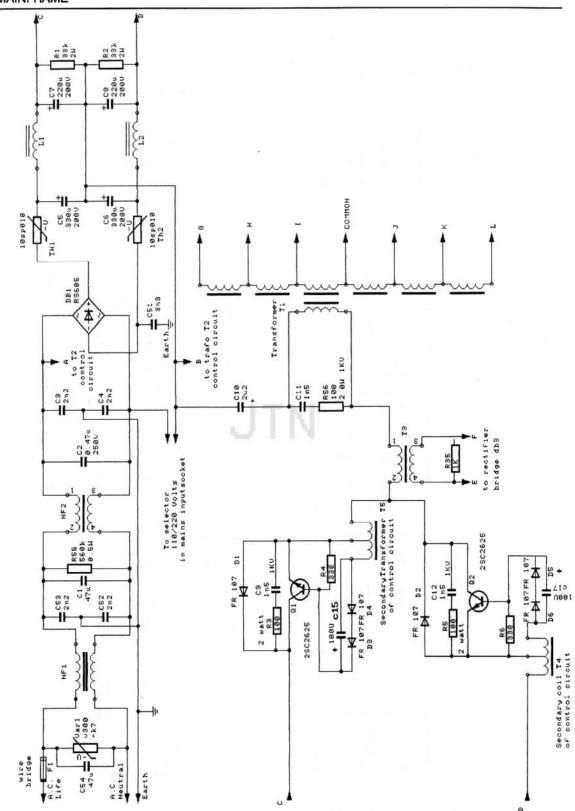

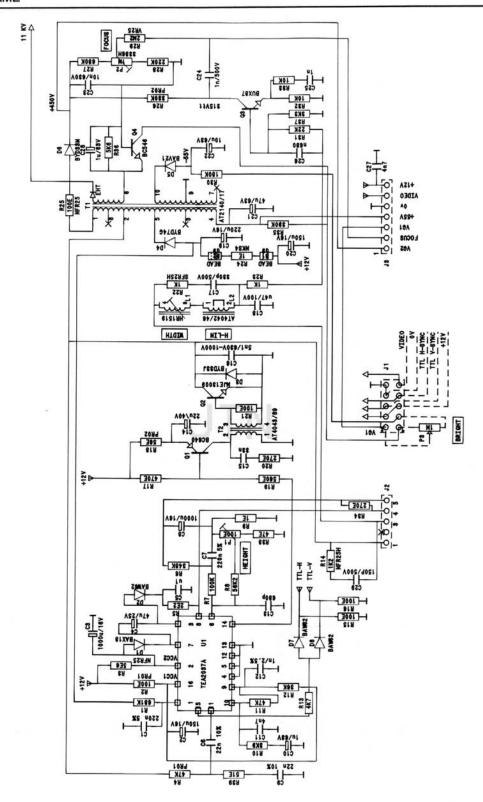

Fig. 3.2. Drawing Primary Circuit.

#### 3.2.2 Circuit description.

#### 3.2.2.1 The primary circuit.

The mains voltage is filtered by coils NF1 and NF2 as well as capacitors C1, C2, C3, C4, C52 and C53.

This voltage is rectified by rectifier bridge DB1.

The inrush current suppressors TH1 and TH2 protect the input circuitry against too high inrush current during power on of the instrument.

The smoothed primary voltage is fed to the chopper FET's Q1 and Q2.

These FET's will cut (with a certain frequency) the primary voltage in parts. The width of these parts (energy contents) is determined by the *pulse width modulator* (PWM) IC1 of control circuit 1. To protect Q1 against high flyback voltage peaks the following protection components are used: D1, C9, R3, C15, D3 and D4. The same protection principle is used for Q2.

Transformer's T4 and T5 are the control transformers through which the square wave control voltages are sent from the PWM to the chopper FET's.

The chopped primary voltage is sent to transformer T1. The secondary coils of this transformer supply the +12V ,+5V and -5V unrectified ac voltages.

In this way the primary mains voltage is separated from the secondary side.

To sense the primary current through transformer T1 a current sense transformer T3 is connected in series. Its secondary side is connected to the control section of the PWM.

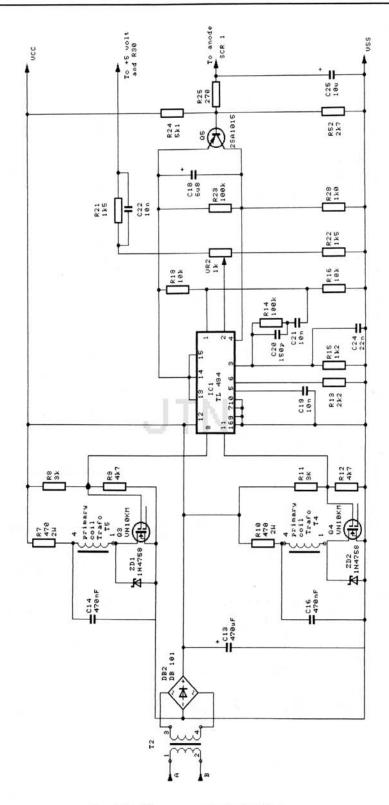

### 3.2.2.2 The control circuit 1.

This circuit mainly controls the primary circuit with IC1.

IC1 is a switch mode pulse width modulation circuit.

It contains an on chip oscillator, dead time control stage, error amplifier, +5V reference circuit and a push-pull output stage.

Via resistors R21, R22 and VR2, the +5V output voltage of the power supply is compared with the internal reference voltage of IC1.

Pin 1 and 2 of IC1 are inputs of the internal error amplifier to which VR2 and joint R18, R16 are connected.

Pin 14 delivers the reference +5V to R18. Now a voltage of 2.5V will appear on the joint of R18, R16

The voltage difference between the wiper of VR2 and joint R18, R16 (the error voltage) is amplified by the error amplifier to correct the pulse-width of the output stage, controlling the primary choppers.

In this way a stabilization is realized.

The frequency  $(\pm 50 \text{ kHz})$  of the output pulses (chopping rate) is determined by R13 and C19. Pin 3 is used as feedback input for the comparator of the PWM, and pin 4 is connected to a dead time control stage.

When this control stage is activated via transistor Q5 the PWM will switch off.

The push-pull outputs pin 8 and pin 4 of IC1 contain a mutually 180 degrees shifted output block pulse.

These block pulses are sent to Q3 and Q4 to switch the primary coils of driver transformer T4 and T5.

Fig. 3.3. Diagram control circuit 1.

Fig. 3.4. Diagram control circuit 2.

#### 3.2.2.3 The control circuit 2.

This control circuit contains of the secondary stage (current and voltage sensors) and a block of safety protection circuitry.

### Secondary stage.

The secondary side of transformer T1 supplies the 3 output voltages for the +12V, +5V and -5V.

The 12V output.

The output voltage of coil G-L is rectified by diodes D7a and D7b.

A high frequency stop filter is formed by L5, C32, C37, L6 and C35 to block the high frequency chopping transients. By means of potentiometer VR1 the controllable zener diode SHR1 is set to approximately 12.7V. Transistor Q3 will boost this voltage to be a smoothed +12V at 2A rate available at pins 11 and 12 of J2.

An **over-current sense** in this output is achieved by resistor R49 and transistor Q9. Via the PWM the power supply is shut down as soon as an over-current situation occurs.

The +5V output.

The output voltage of coil I-J of T1 is rectified by the diodes D8a and D8b. Filtering of high frequencies is accomplished by coil L3 and L4. The smoothing of the output voltage is done with a series of capacitors i.e C36, C40, C42, C43 and C45. There is no serial regulator because of the high current rate of 20A. The stabilization of the output voltage is controlled by the PWM via resistors R21, R22 and the potentiometer VR2. Over-current in this circuit is sensed by T3 in the primary circuit.

The -5V output.

The output voltage of coil H-K of T1 is rectified to a negative voltage by diodes D9a and D9b and filtered by L7, C39, L8 and C41.

Stabilizer IC2 will offer an accurate -5V which is boosted by transistor Q14 to a 3A rate.

## The safety protection's

The heart of the **safety protection circuits** consists of thyristor SCR1.

If this thyristor is activated, the PWM will be shut down, and the power supply switched off.

The +5V and -5V are sensed by safety circuits for over-voltages. Potentiometer VR3 can be aligned in such a way that the thyristor SCR1 is only triggered via ZD3 and D10 if the +5V raises above +5.6V.

Potentiometer VR4 does the same for the -5V output. To obtain a trigger-pulse with a positive polarity for the thyristor, the -5V over-voltage must be inverted. This is obtained via Q10, Q11 and Q12.

To the gate of thyristor SCR1 the primary current sense transformer information is also connected. The higher the primary current, the higher the rectified output voltage of rectifier DB3. By this there is a linear relation between this rectified voltage and the total secondary current in the power supply. The total power supplied to the secondary circuit before shutdown takes place can be set by R26.

Over-current situations in the +12V are sensed by the thyristor via R49, Q9 and R20 and in the -5V by R48, Q8, R31, Q7 and R34.

An extra protection for excessive temperature is achieved via components Q6, R53 and D12. These components activate the thyristor when either the **thermal switches** on the analyzer main-board or the thermal switch on the chopper heatsink shorts R51 to ground.

For alignment of all potentiometers see chapter "Alignments".

#### FLOPPY DISK DRIVE. 3.3

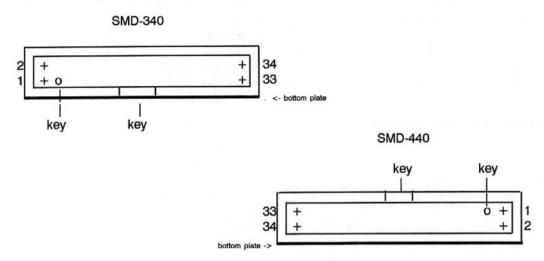

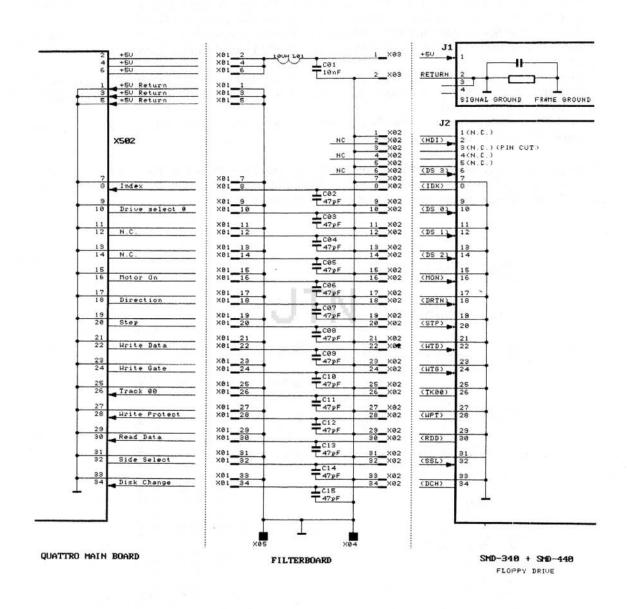

The floppy disk drive used is the Epson SMD-340 or SMD-440L super thin 3.5 inch double sided type. Both types are interchangeable and have the same specifications. The only difference is the placement of the flat ribbon cable to the unit. In the SMD-340 this cable is turned 180 degrees compared to the SMD-440L. The cable is key protected in both types.

## 3.3.1 Drive Performance Specifications.

| Single 5V power supply                |                 |

|---------------------------------------|-----------------|

| Capacity (MFM recording) high density | 1474K-bytes     |

| Number of tracks                      | 80 per surface  |

| Maximum recording density             | 17434 bits/inch |

| Track density                         | 135 track/inch  |

| Transfer rate                         | 500K-bits/s     |

| Average latency                       | 100ms           |

| Access time (track to track)          | 3ms             |

| Settling time                         | 15ms            |

| Motor start time                      | 0.5s            |

| Disk rotation speed                   | 300rpm          |

## 3.3.2 Drive Reliability.

10,000 power on hours Mean Time Between Failures Error rates 1 per 1,000,000,000 Soft error rate

Hard error rate

Seek error rate

1 per 1,000,000,000,000 1 per 1,000,000

#### Electronic Circuitry. 3.3.3

A custom made CMOS chip contains all the logic circuitry. Analog circuitry is also integrated within a single chip operating at +5V.

The main control and read/write circuits are contained on the main-control circuit board. The spindle motor circuit is integrated within the motor control circuit board.

The control circuit consists of:

- read/write logic and amplifier 1.

- stepper motor control circuit 2.

- spindle motor control circuit 3.

- side select circuit 4.

- mode select circuit 5.

- track 00 detection circuit 6.

- index detection circuit 7.

- 8. write protect sensor circuit

- 9. cartridge-in sensor control circuit

- density detection circuit 10.

Due to the complexity and high integration rate of the floppy-drive, the unit can only be replaced locally in case of malfunctioning.

There are no field adjustable items or replaceable parts.

The unit must be replaced if faulty.

## 3.3.3.1 Drive Connectors.

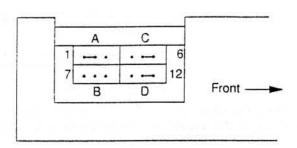

Power connectors both types.

The small 4-pole power connector is of a key-lock insertion type. Pin 1 is connected to the +5 volt and pin 2 to ground. Pin 3 and 4 are not connected.

Layout:

Signal connector.

The signal connector is a 34 pole type and keyed on the top.

All data and control signals are passed through the flat ribbon cable connected to this connector.

The pin assignment is as follows:

| PIN                              | SIGNAL NAME           |

|----------------------------------|-----------------------|

| 1. Pu                            | N.C.                  |

| 2.                               | High Density In (HDI) |

| 3, 4, 5, 6.                      | N.C.                  |

| 7, 9, 11.                        | +5V                   |

| 8.                               | Index pulse out (IDX) |

| 10.                              | Drive select 0 (DS0)  |

| 12.                              | Drive select 1 (DS1)  |

| 13,15,17,19,21,23,25,27,29,31,33 | Ground                |

| 14.                              | N.C.                  |

| 16.                              | Motor On (MON)        |

| 18.                              | Direction (DRTN)      |

| 20.                              | Step (STP)            |

| 22.                              | Write Data (WTD)      |

| 24.                              | Write Gate (WTG)      |

| 26.                              | Track 00 (TK00)       |

| 28.                              | Write Protect (WPT)   |

| 30.                              | Read Data (RDD)       |

| 32.                              | Side Select (SSL)     |

| 34.                              | Disk Change (DCH)     |

|                                  |                       |

The connector layout:

Care must be taken when the drive is exchanged to ensure that the flat ribbon connector is inserted correctly, according to the key holes, into the frame of the drive.

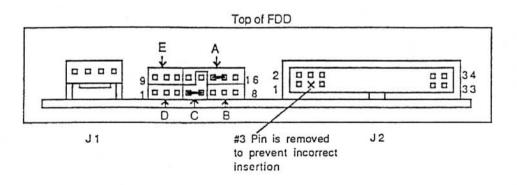

## 3.3.4 Setting the jumpers on a replacement floppy drive.

The replacement floppy disk drive should have been received by the customer with the standard settings that are required for use with the PM 3580/PM 3585 logic analyzers. Check for correct floppy drive jumpersettings before installing the new drive as a replacement unit.

## 3.3.4.1 SMD-340 Jumper settings.

Fig. 3.5. Location of the jumper block of the SMD-340.

| Block | connection | function                               |

|-------|------------|----------------------------------------|

| A     | 14 - 15    | Drive select 0                         |

| В     | -          | No connections                         |

| С     | 4 - 5      | Mode change caused by internal sensors |

| D     | #          | Not relevant, not used                 |

| E     | <u> </u>   | Not relevant, not used                 |

## 3.3.4.2 SMD-440 Jumper settings

Fig. 3.6. Location of the jumper block of the SMD-440.

| Block   | connection | function                               |

|---------|------------|----------------------------------------|

| A Block | 1 - 2      | Drive select 0                         |

| B Block |            | No connections                         |

| C Block | 5 - 6      | Mode change caused by internal sensors |

| D Block |            | Not relevant                           |

Fig. 3.7. Floppy disk drive interconnections.

## 3.4 KEYBOARD.

The keyboard is a stand alone unit based on the piggy-back programmed micro-controller 8400 family from PHILIPS.

The micro-controller used is the 84C01 and operates at a 4 MHz speed.

This controller has several 8-bit i/o ports as well as an I<sup>2</sup>c communication interface. This communication interface is used to communicate with the analyzers main-board.

The micro-controller is programmed to continuously scan the keys which are mounted in a matrix of horizontal and vertical lines. The horizontal lines are connected to Port 1 and the vertical lines to Port 2.

If a key is depressed a short is made via the key-contact between a certain horizontal line and a vertical line. By decoding which horizontal and which vertical line is involved the micro-controller can identify the key pressed.

By looking up the key-code in the PROM-key-table the correct ASCII code can be found and transmitted to the main-board via the I<sup>2</sup>c bus.

The dial key will generate 2 phase-shifted pulses which are analyzed by the micro-controller to determine the direction the dial was moved in. These phase shifted pulses are connected to pin 1 of Port 2 and timer-interrupt input T0 of the micro-controller.

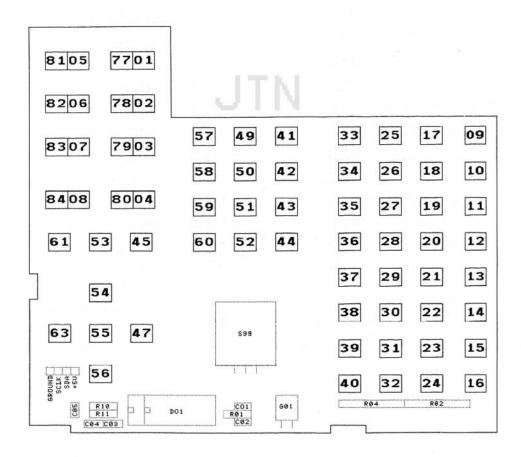

Fig. 3.8. Unit drawing keyboard.

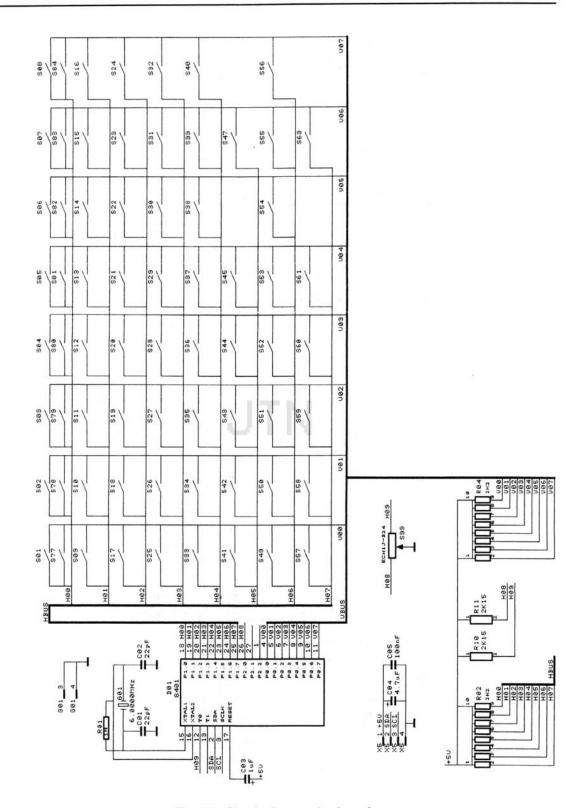

Fig. 3.9. Circuit diagram keyboard.

Fig. 3.10. Circuit diagram monitor control board.

## 3.5 VIDEO MONITOR.

## 3.5.1 General information.

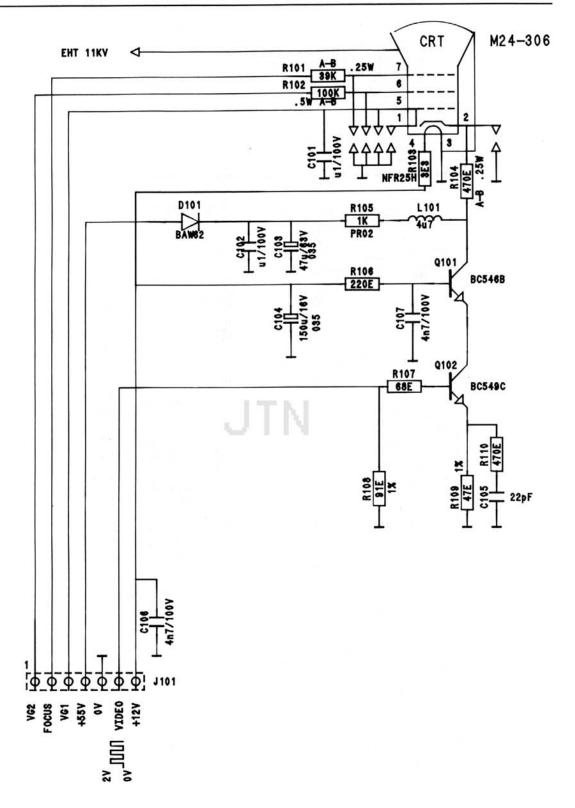

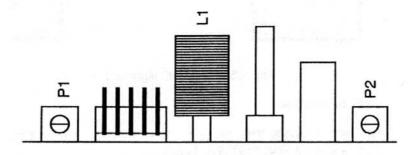

The video monitor used is composed of a monitor control board attached to the analyzers chassis, a CRT board pressed on the picture tube and the picture tube itself.

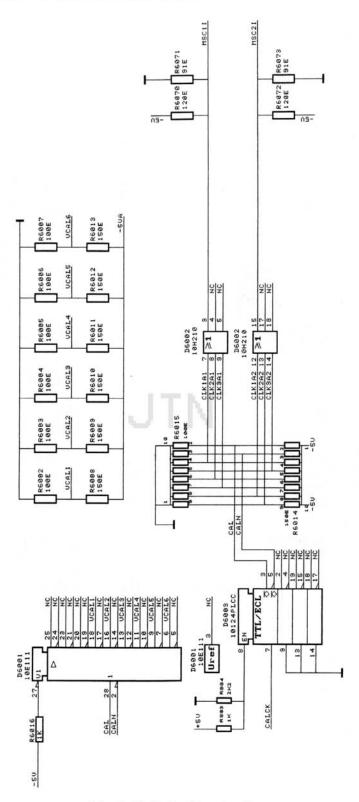

The control signals (VSYNC an HSYNC) and power supply (+12V) of the video monitor are all supplied via the 10-pole flat cable coming from the analyzers main-board.

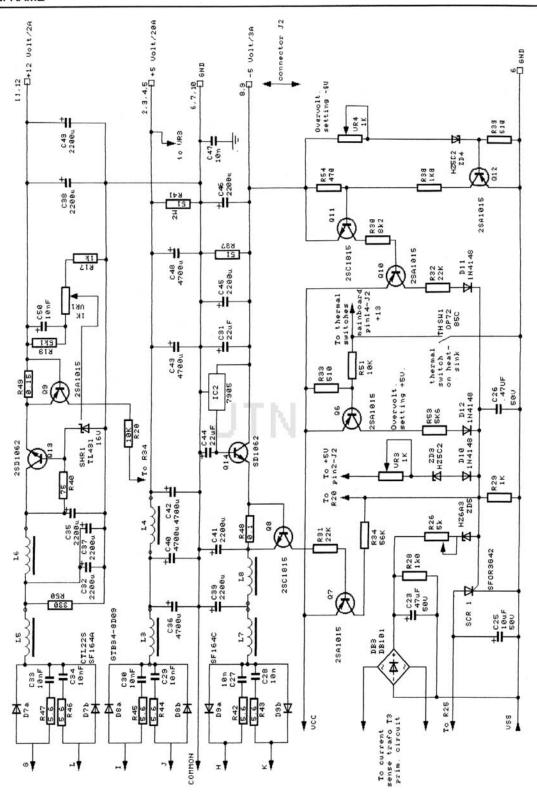

## 3.5.2 Circuit description.

The control board has three main units i.e.

- 1. Vertical synchronization and deflection circuit.

- 2. Horizontal synchronization and deflection circuit.

- 3. Brightness and E(xtremely) H(igh) T(ension) circuitry.

The items 1 and 2 are all included in I.C. U1 the TEA2037A. This IC contains:

- 2 free running oscillators (vertical 60 Hz and horizontal 31 kHz)

- a combined sync input followed by sync separator

- a horizontal driver stage

- a vertical output to directly drive the deflection coil

The oscillators are individually triggered by the sync signals coming from the analyzers main-board via connector J1.

Potentiometer P1 sets the vertical deflection amplitude and hence the *hight of the video picture*. The horizontal output of U1 is used to drive the line transformer via Q1 and Q2. The line transformer supplies the EHT and focus voltage.

The focus of the video picture is factory set by potentiometer P2.

The CRT board is connected with a flat ribbon cable to the monitor control board. On the CRT board the video output stage is mounted (transistors Q102 and Q101) as well as some safety bridges for the various picture tube control voltages.

The picture tube's filament is directly heated from the 12V power supply via a resistor of 3.3a

On the picture tube the deflection units are mounted as well as a set of **static deflexion rings** to align the picture to the centre of the tube.

For all alignments refer to chapter 4 "Adjustments and jumpersettings"

JTN

Fig. 3.11. Circuit diagram CRT board.

Fig. 3.12. Unit drawing video monitor.

## 3.6 FAN UNIT.

Electronic circuitry in the fan unit itself is responsible for a stable rotating magnetic field and hence a smooth running of the fan.

The fan unit runs on the +12V from the analyzers main board.

# 3.7 MAIN-BOARD HARDWARE DESCRIPTION.

## 3.7.1 General structure main-board.

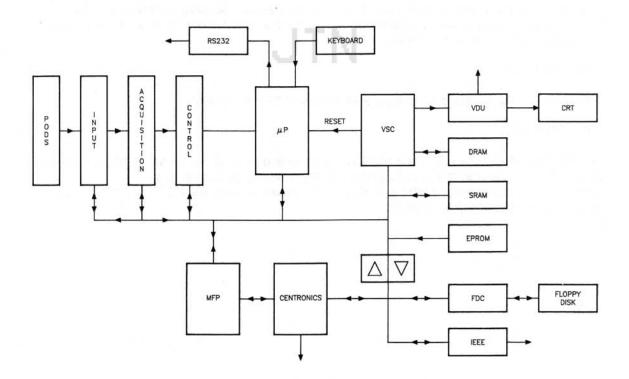

The following diagram shows the general structure of the analyzer main-board.

Fig. 3.13. General structure of Analyzer main-board.

## 3.7.2 The different boards.

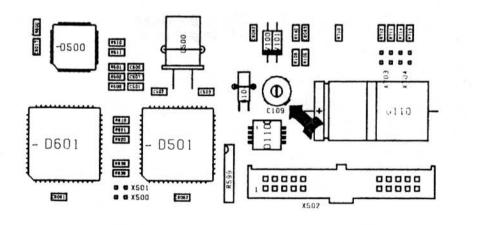

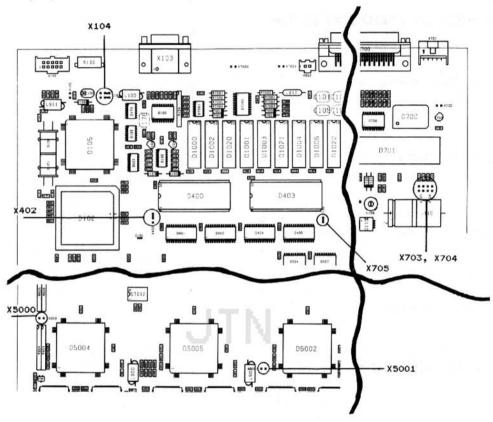

There are two different layout's, the 200 MHz board and the 100 MHz board.

The 200 MHz board can be equipped with 96 channels (fully filled) or 64 channels (partly filled board).

The 100 MHz board has a different layout compared with the 200 MHz board and can be equipped with 64 channels (fully filled) or 32 channels (partly filled board).

The chart shows the 4 different boards and their abbreviation names :

| 200 MHz 96 channels | <ul> <li>296 board</li> </ul> |

|---------------------|-------------------------------|

| 200 MHz 64 channels | <ul> <li>264 board</li> </ul> |

| 100 MHz 64 channels | - 164 board                   |

| 100 MHz 32 channels | <ul> <li>132 board</li> </ul> |

### - The 296 board.

This board is fully equipped to support a 96 channel 200 MHz analyzer.

#### - The 264 board.

The 200 MHz 64 channel board is a 200 MHz 96 channel board without X5, X6, D5004, D5005, D9, D10, D11, D12 latch D307 and several other small components like resistors and capacitors. On this board jumpers X5000 and X5001 are present to short the BST chain for the absent Acquisition ASIC's D5004 and D5005.

## - The 164 board.

This board is fully equipped to support a 64 channel 100 MHz analyzer.

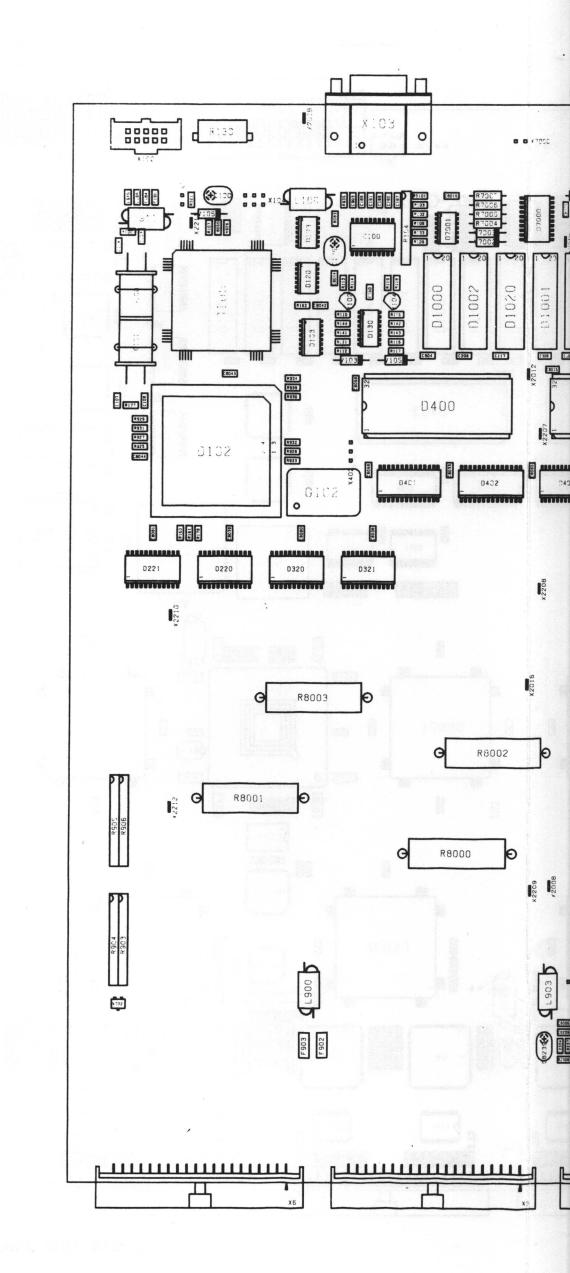

#### - The 132 board.

The 100 MHz 32 channel board is a 100 MHz 64 channel board without X3, X4, D5002, D5003, D5, D6, D7, D8 and several other small components like resistors and capacitors. Also on this board jumpers X5002 and X5003 are present to short the BST chain for the absent Acquisition ASIC's D5002 and D5003.

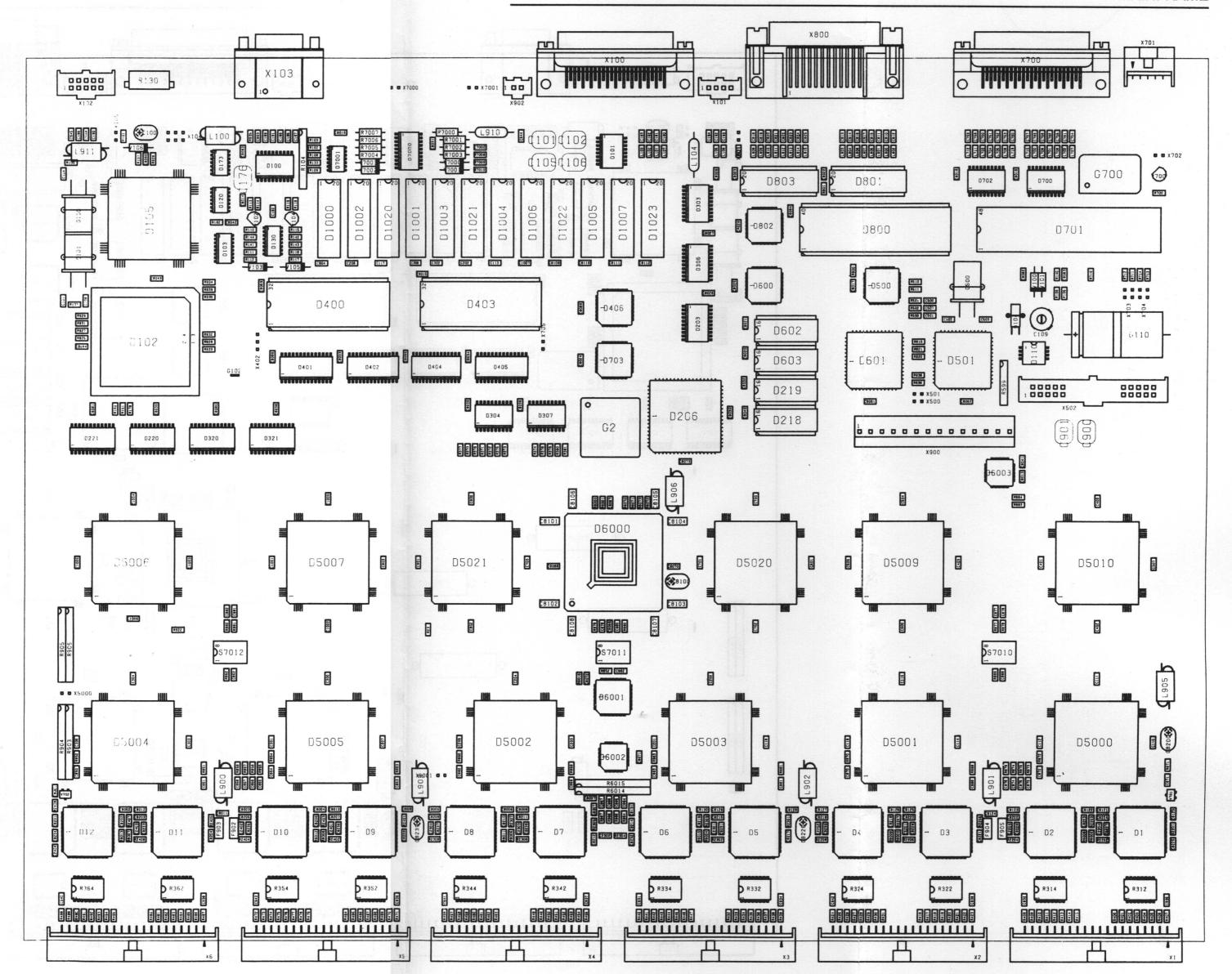

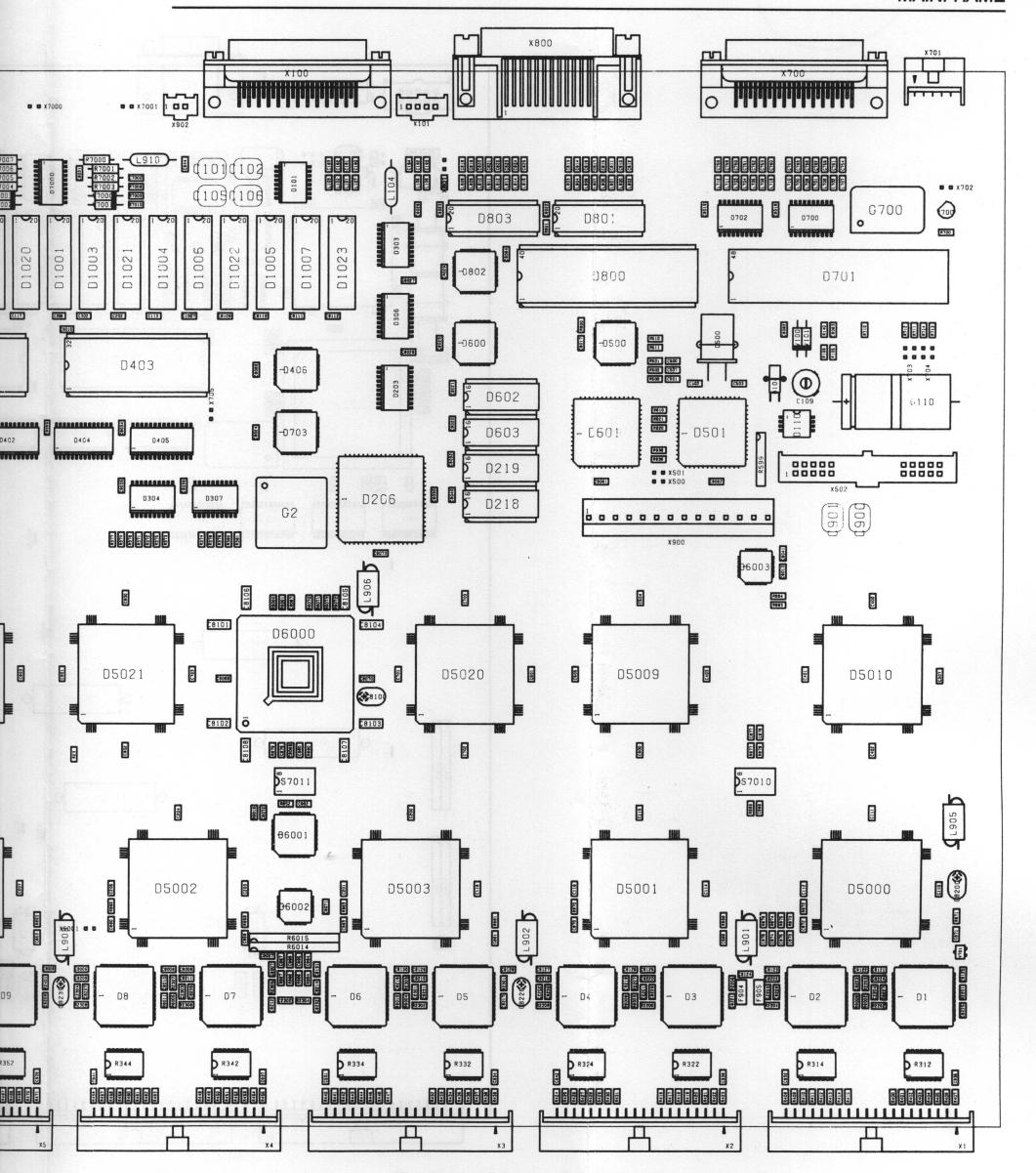

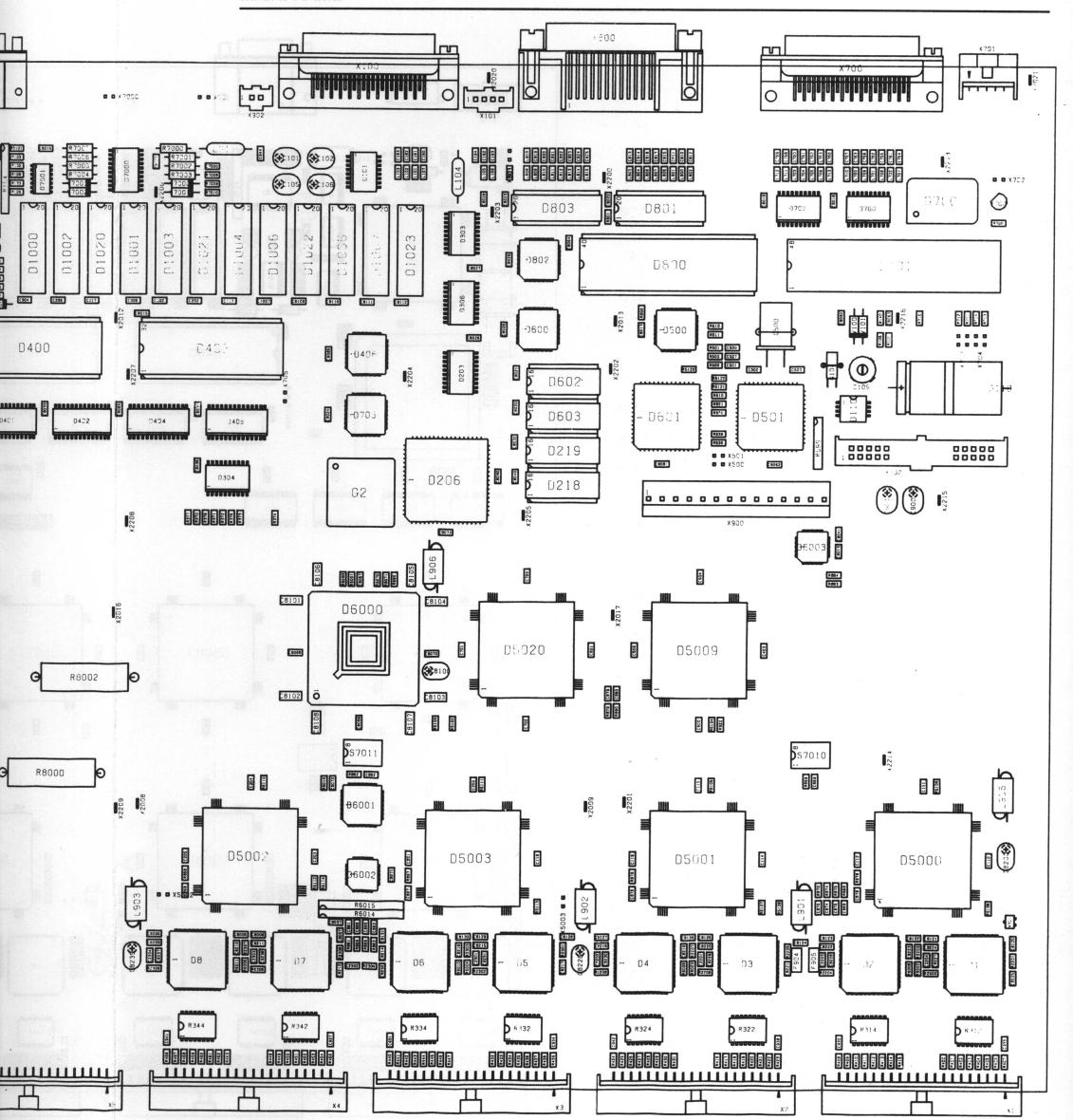

Fig. 3.14. Unit drawing 200 MHz main-board.

Fig. 3.14. Unit drawing 200 MHz main-board.

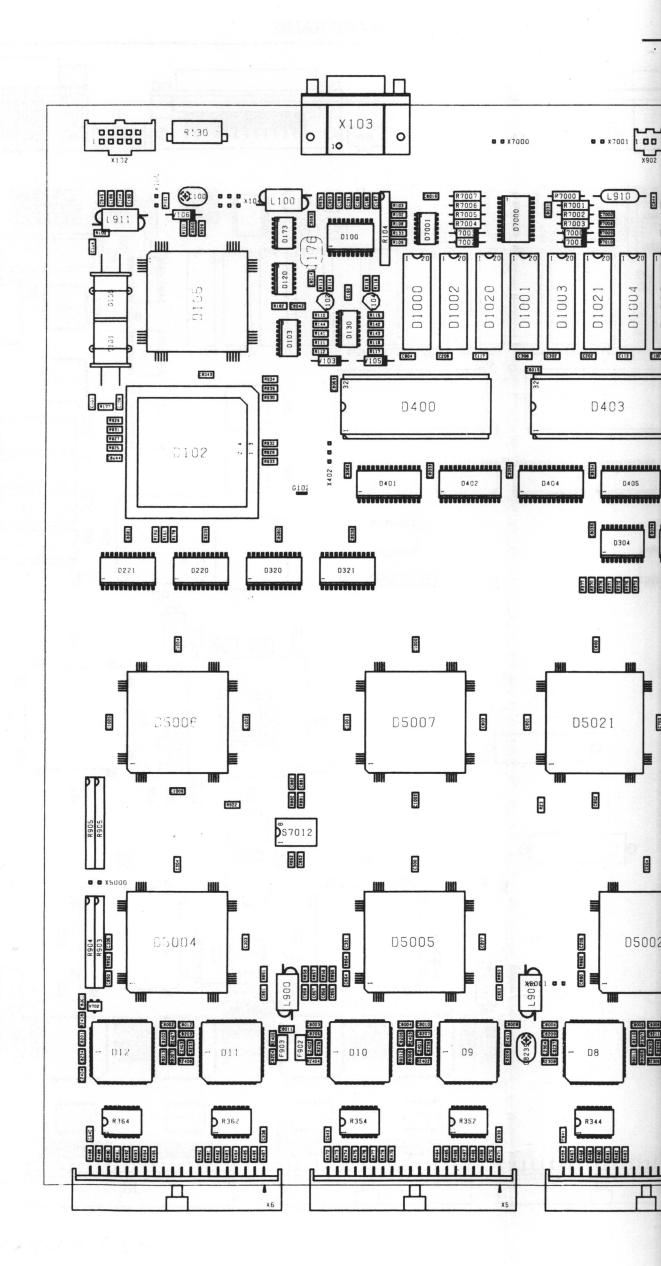

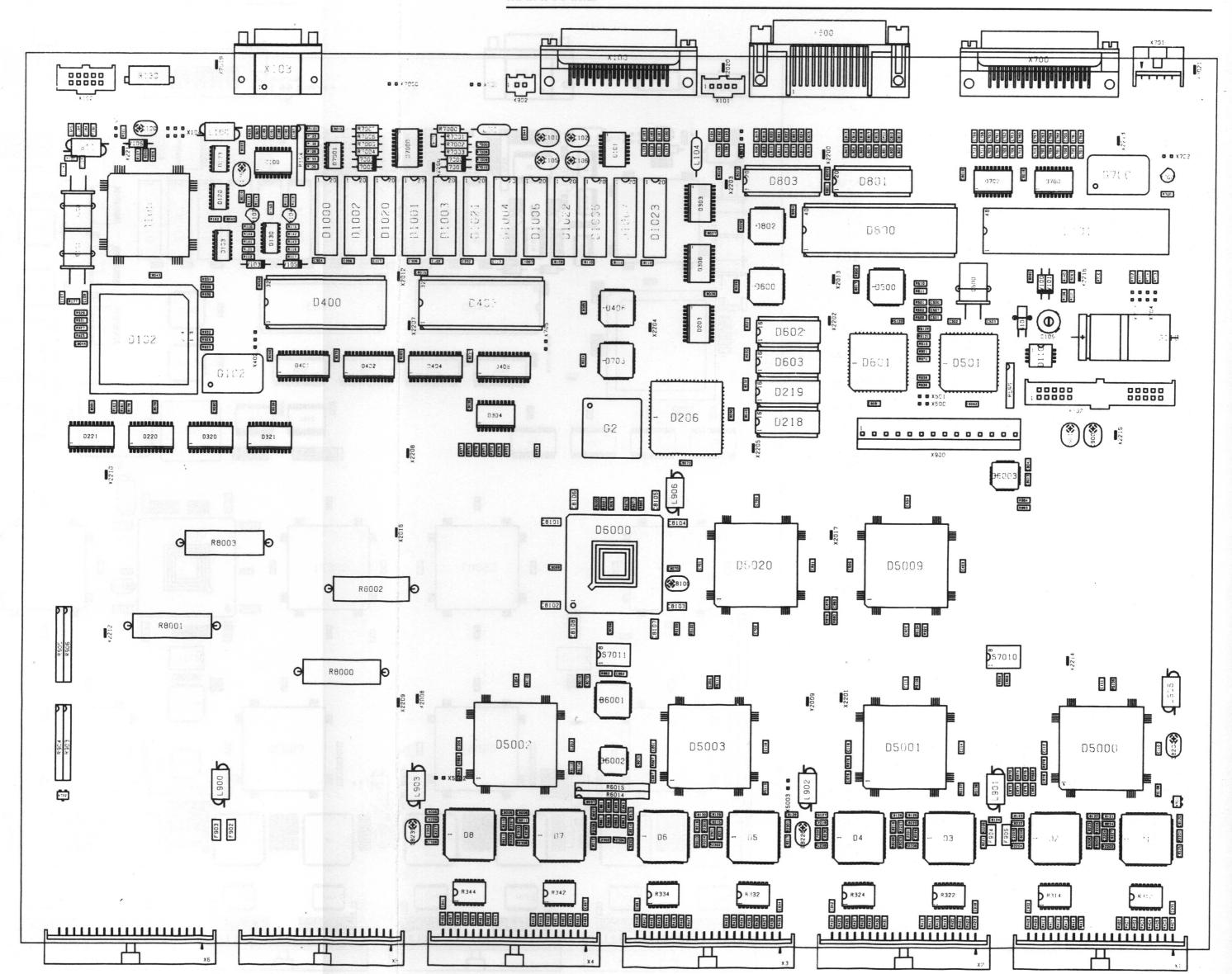

Fig. 3.15. Unit drawing 100 MHz main-board.

Fig. 3.15. Unit drawing 100 MHz main-board.

## 3.7.3 The CPU section.

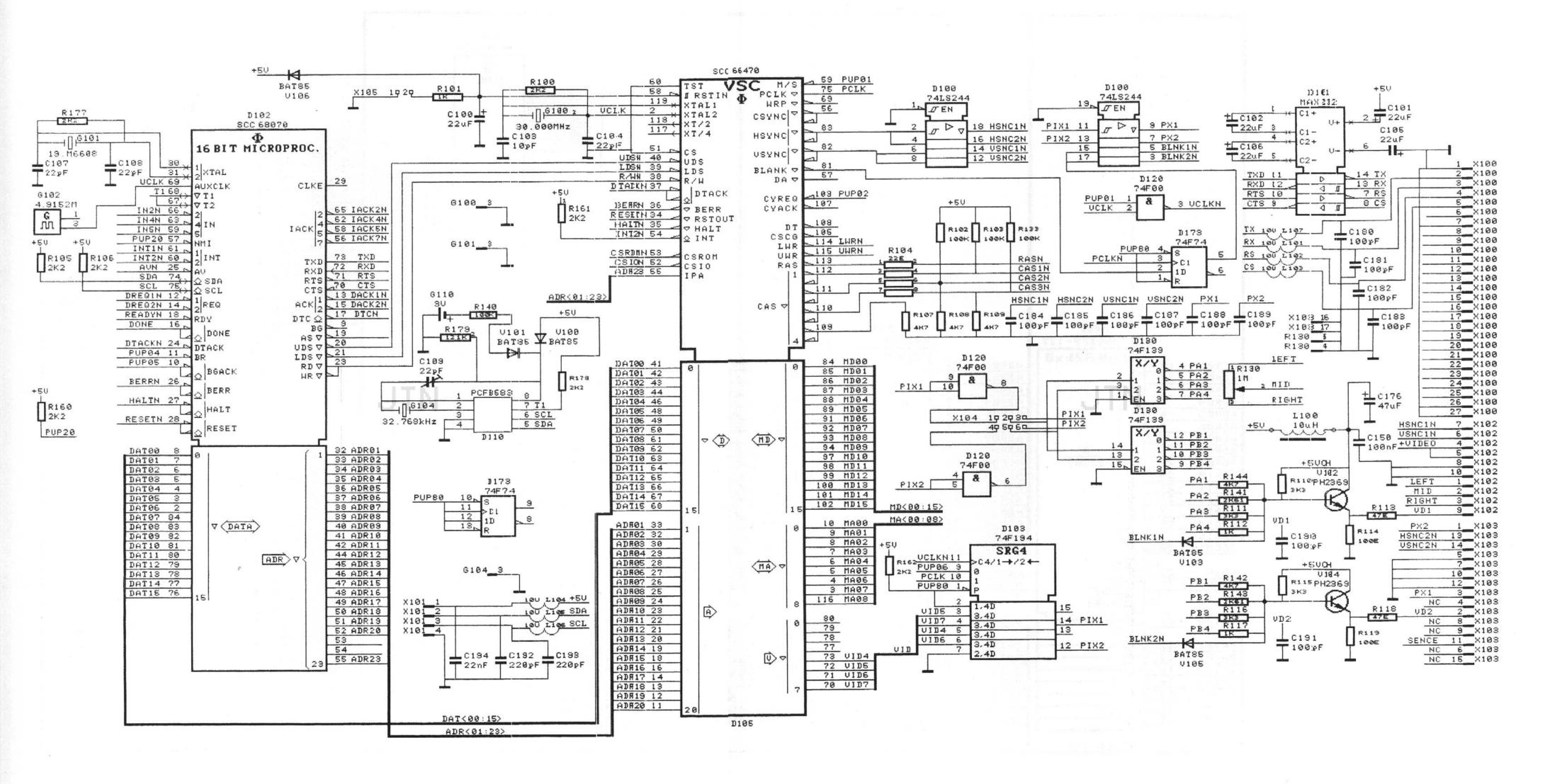

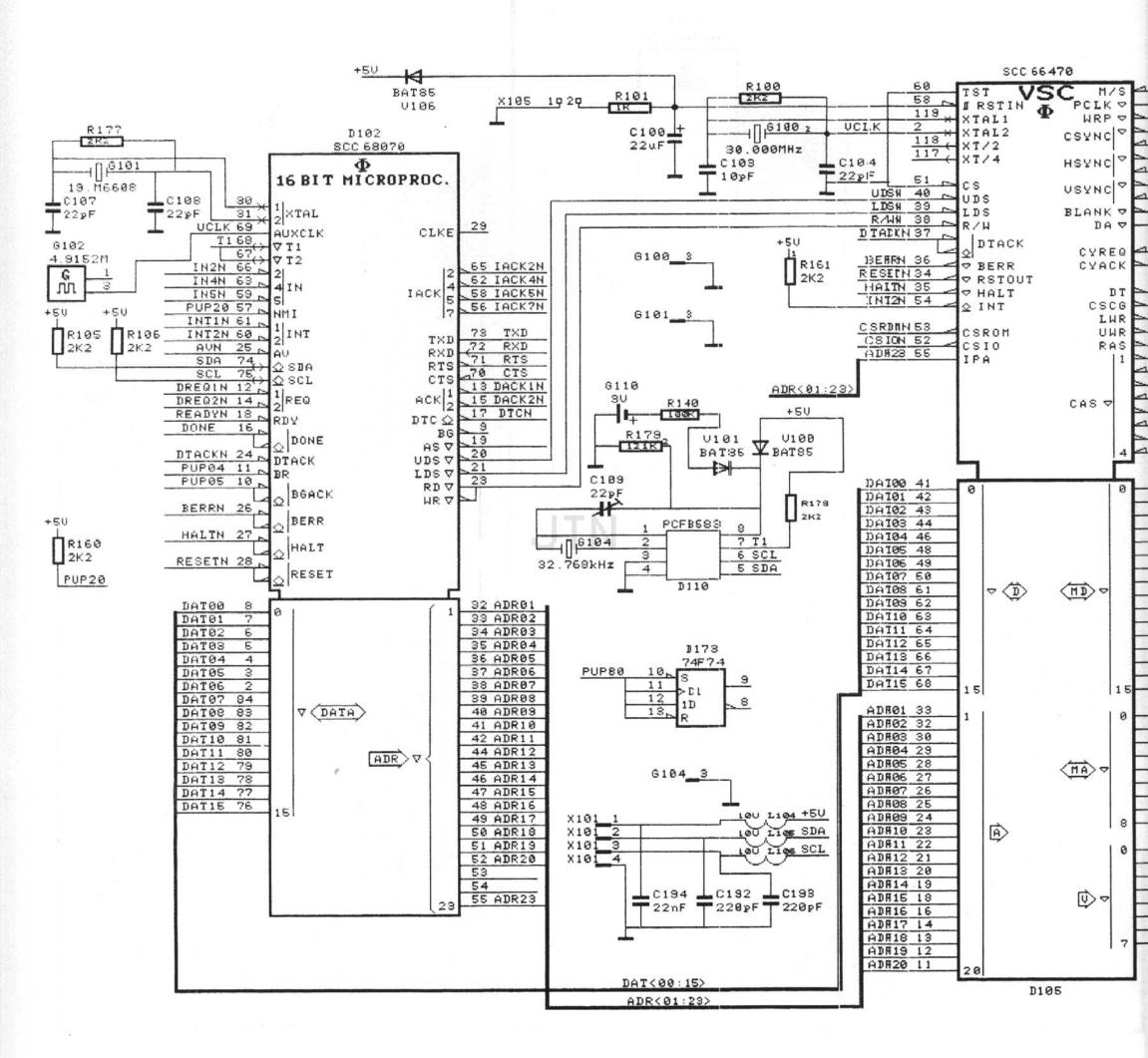

Refer to Fig. 3.16.

The 68070 microprocessor (D102) is a 16 bit processor operating at a 19.6 MHz clock speed. It has on chip DMA control, Memory Management Unit, I<sup>2</sup>c bus drive section, built-in timer and a RS232 device.

The 19.6 MHz clock is derived from the xtal G101 and divided by 2 by the CPU to generate 10 MHz bus cycles. The 68070's external bus has 23 non-multiplexed address lines capable of addressing a 16M-byte address range and 16 bit data lines.

There are 7 interrupt levels of which four are decoded interrupts with separate acknowledge outputs IACK2N, 4N, 5N and 7N. Two DMA channels are also available of which only DREQ1N is used for the disk drive.

In order to obtain a proper baud-rate frequency for the RS232 serial output the frequency of G101 is divided by the correct value. G102 is used for baud-rate calculations in future options.

The  $l^2c$  bus is used to communicate with the keyboard interface and the real time clock chip. This universal bus is connected to the keyboards 8400 microprocessor which has its own on chip  $l^2c$  control device.

The I2c bus signals are SDA (serial data) and SCL (serial clock).

At Power-On the 68070 is reset by the Video and System Controller SCC66470 (D105). This chip is reset by capacitor C100 or manually via the link X105.

The VSC is a C-MOS 680xx family display and system controller. It can directly drive up to 2M-bytes of memory and provides chip-select signals for system ROM (D400 and D403). The System ROM is enabled with the signal "CSROM" and the peripherals are enabled with the signal "CSIO".

The on-chip DRAM controller controls 1.5M-byte DRAM (D1000 to D1007 and D1020 to D1023). The CPU can access any memory location even during active video display lines, improving system performance.

The VSC has its own Xtal-frequency of 30 MHz, which is divided by 2 to get the 15 MHz pixel-clock PCLK, and divided by 960 for the 31,25 kHz horizontal synchronisation and divided by 500.000 to get the 60 Hz vertical sync.

The pixel information is clocked by the pixel-clock to the video output VID4-7 on pins 70-73 of the VSC.

These 4 bits comprise 16 grey values on a 15 MHz dot rate. In order to get a 30 MHz dot rate with 4 grey values this 4 bit parallel dot information is clocked with the 30 MHz VCLK through the shift register D103.

The 4 grey values of PIX1 and PIX2 are now demultiplexed by D130 and set to the correct grey value by the attenuator resistor matrix R111, R112, R141 and R144. The video signal is output to the video connector X102 via transistor V102

A corresponding path is used by D100, matrix R116, R117, R142 and R143 and transistor V104 to issue via connector X103 an external video/monitor signal.

After Power-On the VSC is reset and the software will read the 3 CAS inputs (pins 109 to pin 111). Via the pull-up resistors R102, R103 and R133, the CPU can determine how many 512K-byte memory banks are available. The CAS lines are then used as refresh strobe lines for the DRAM's.

Timer IC D110 (PCF 8583) contains all necessary hardware to keep the time and date correct. The Xtal frequency of 32.78677 kHz is divided by 2<sup>15</sup> to interrupt every second the 68070 processor via pin 17. (T1 of D110).

Via the I2c bus the time is sent to the microprocessor.

All the internal RAM, as-well the oscillator circuit of the timer IC, are powered by battery G110 during power off of the analyzer.

3.7.3.1 The RS232 port.

The RS232 port of the CPU is connected to the outside world (X100) by one chip only, the MAX 232 (D101).

This chip generates its own RS232 voltages (-9V and +9V) for line communication via the lines Transmit (TX), Receive (RX), Request To Send (RTS) and Clear To Send (CTS).

Fig. 3.16. The CPU section.

Fig. 3.16. The CPU section.

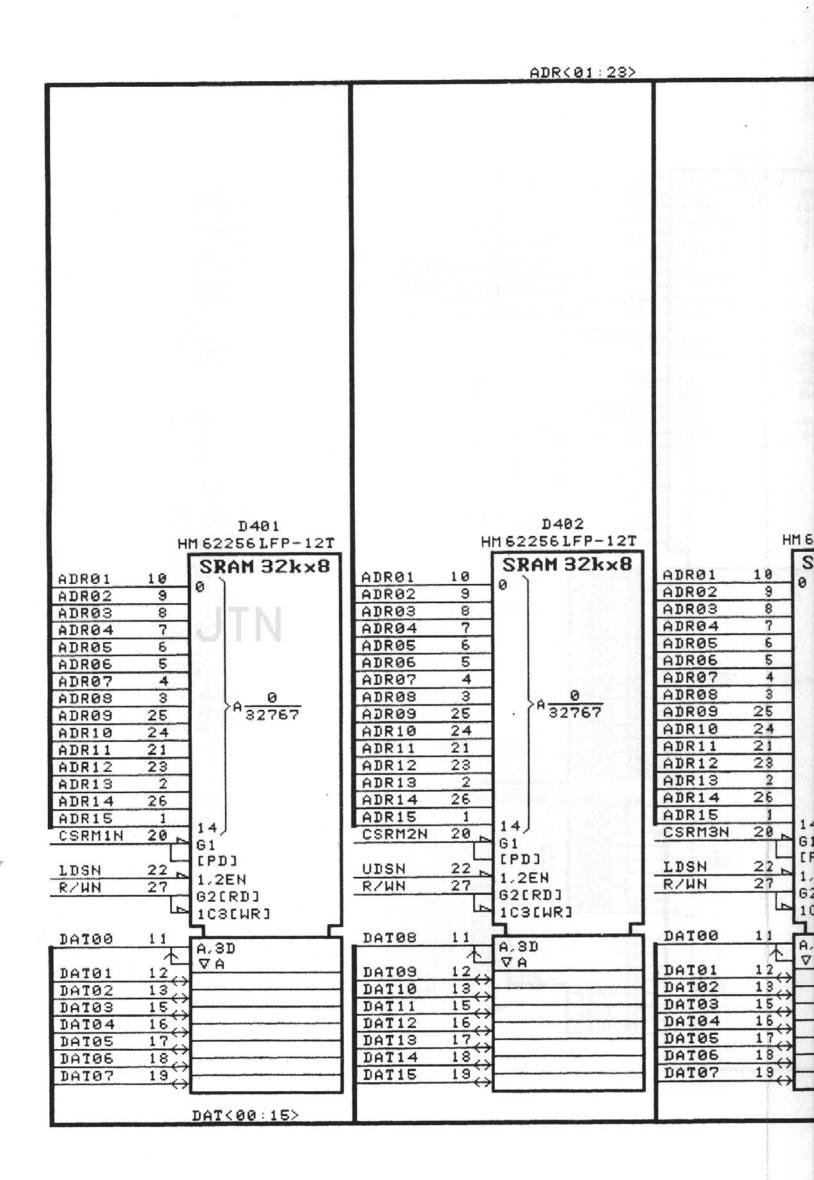

Fig. 3.17. The Static RAM and EPROM.

Fig. 3.17. The Static RAM and EPROM.

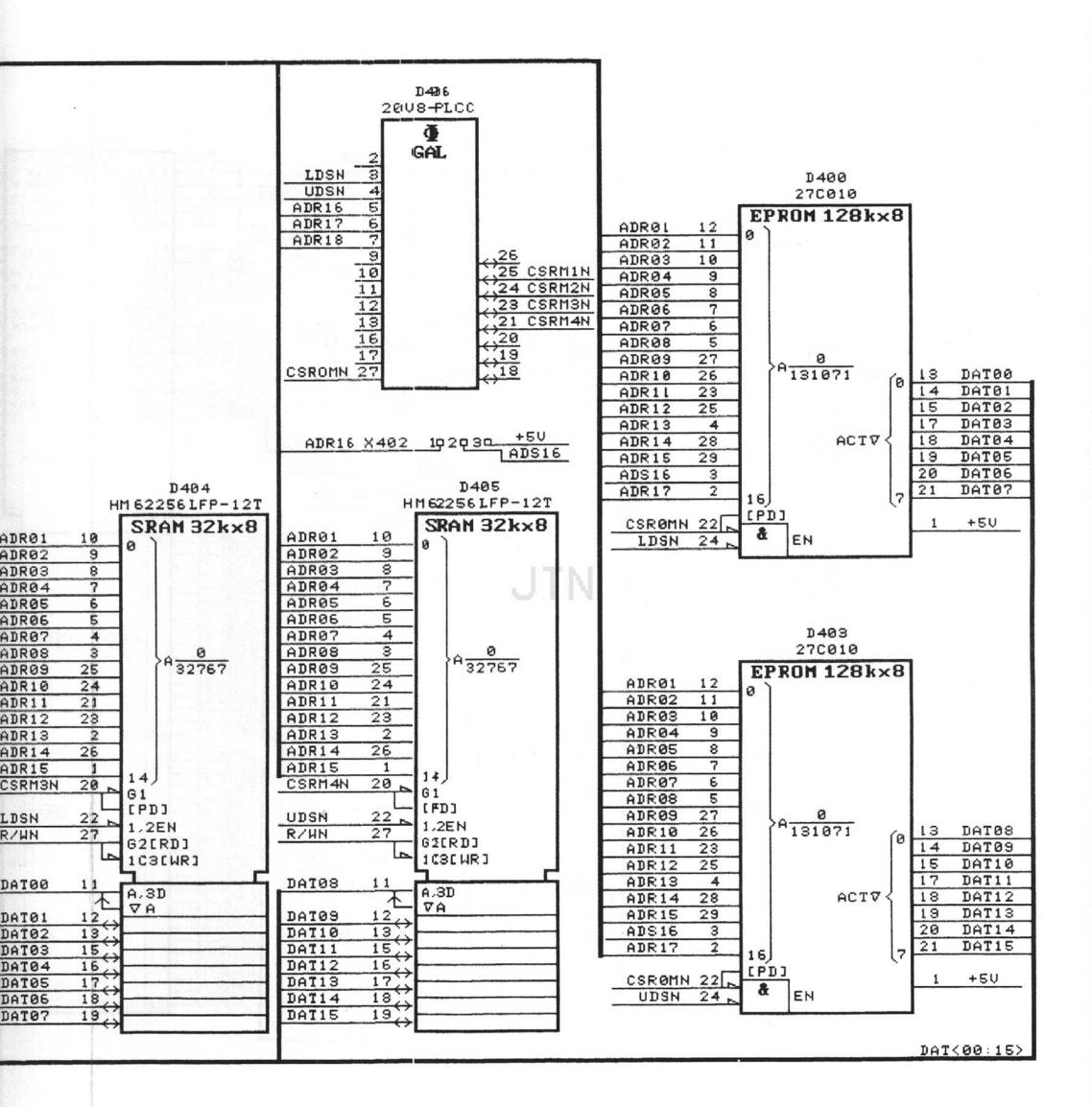

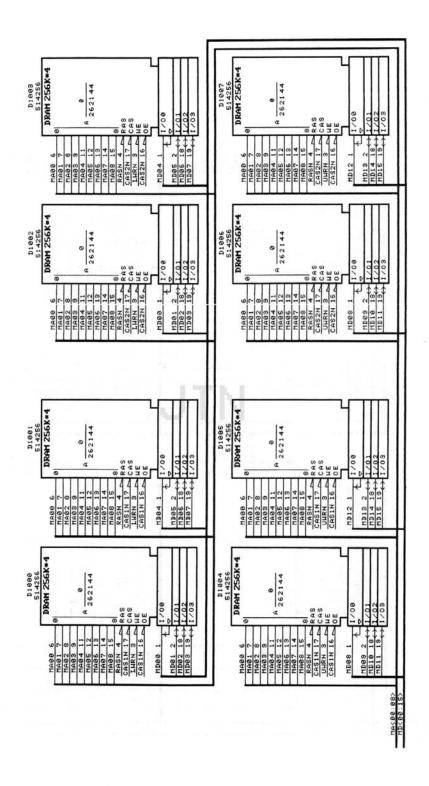

Fig. 3.18. The Dynamic RAM (part 1).

Fig. 3.19. The Dynamic RAM (part 2).

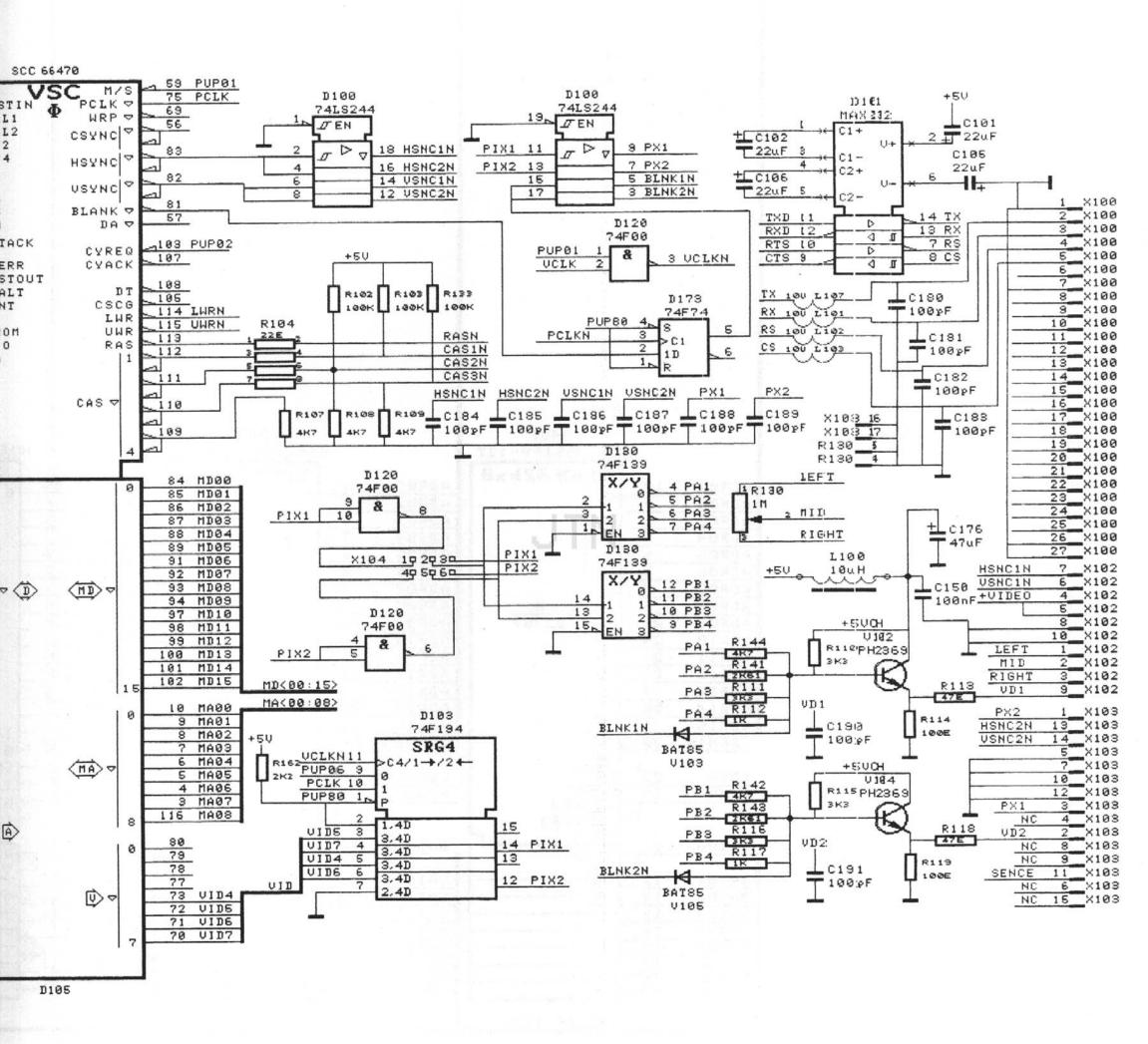

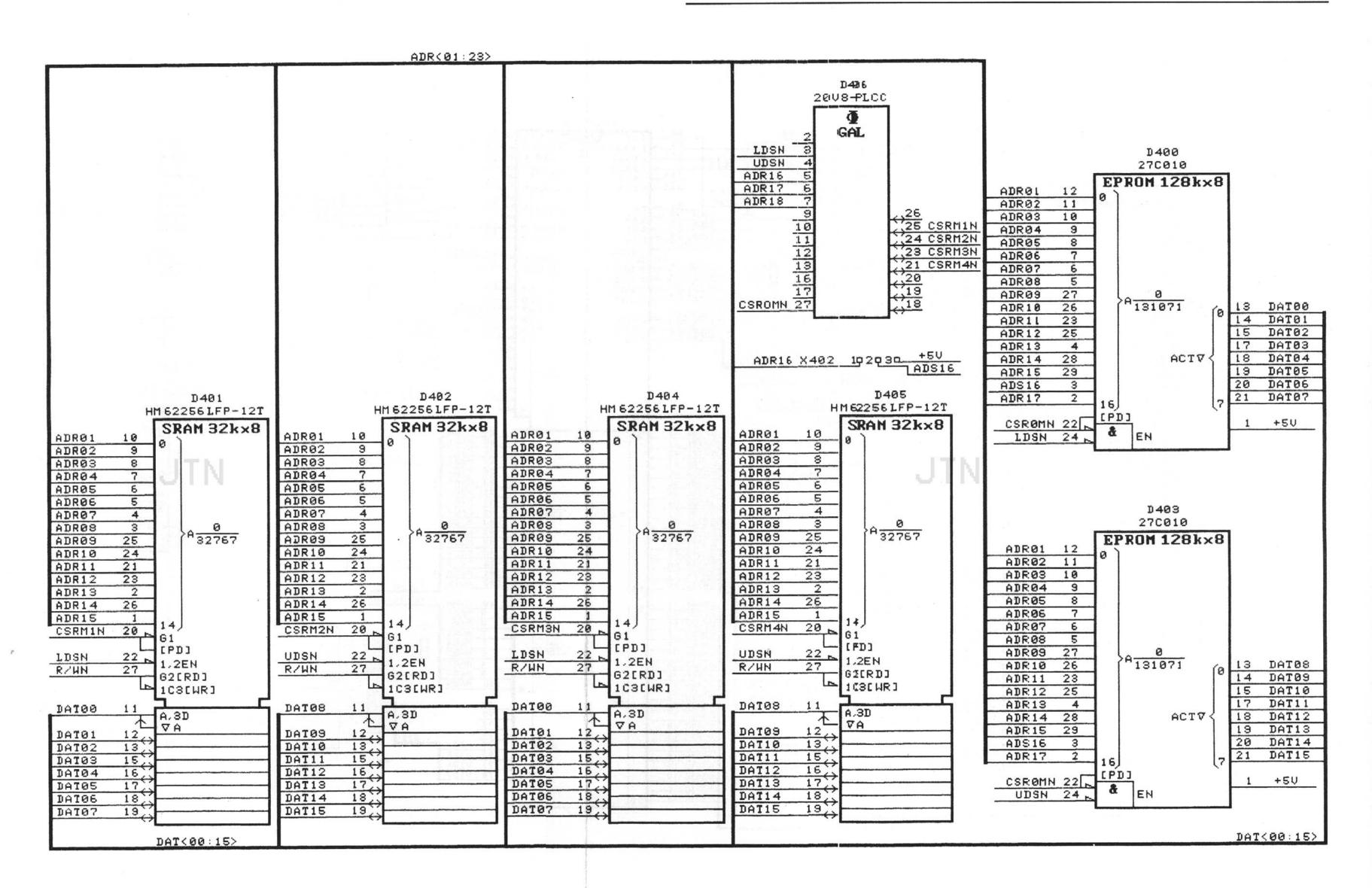

#### 3.7.3.2 The Static RAM.

Refer to Fig. 3.17.

The SRAM's are of the HM 62256LFP-12T type and are 32K-byte x 8 = 256K-bit wide. In total there are 2 banks. Bank1 (D401 and D402) and Bank2 (D404 and D405). Each bank has an odd and an even byte selected by the GAL (Generic Array Logic) address decoding IC D406. Depending on the CPU access, words or bytes are selected.

#### 3.7.3.3 The EPROM's.

Refer to Fig. 3.17.

The resident analyzer software is stored in the 2 EPROM's. These can be any of the following three types; 27256, 27512 or 27010. Depending on the type used, address line ADS16 must be activated and strap X402 must be set accordingly. These settings are:

27256 2-3 connected\* 27512 1-2 connected\* 27010 1-2 connected

\* These types must be positioned to the right-hand side of the socket (towards the battery backup).

The EPROM chip select is derived from a GAL (D703).

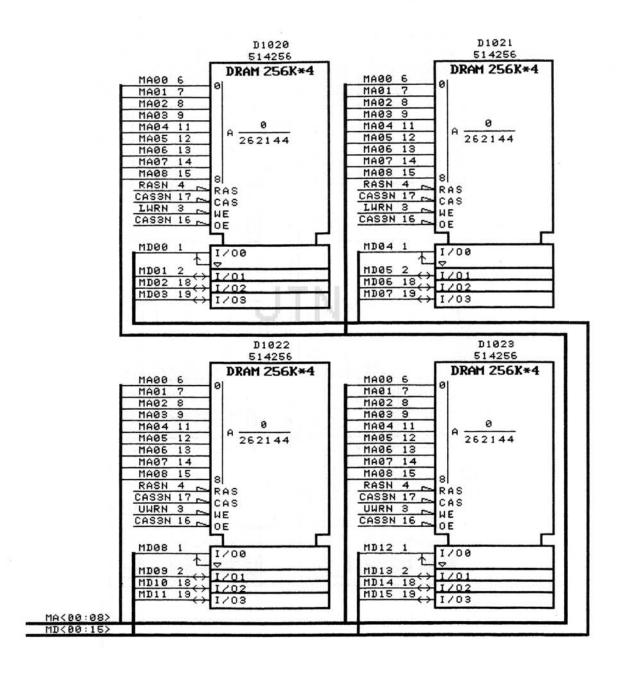

## 3.7.3.4 The Dynamic RAM's.

Refer to Fig. 3.18 and 3.19.

The 3 banks of dynamic RAM's are composed of 4 chips per bank. The RAM chip used is the 514256 (256K x 4 Bits). A RAM can store the high or low nibble in a high or low byte of a word.

UDS and LDS strobes sent from the CPU to the VSC are decoded to UWR (Upper Write Read) for the upper RAM bank and LWR (Lower Write Read ) for the lower RAM bank.

The RAS and CAS signals are timing refresh signals to keep the memory contents refreshed.

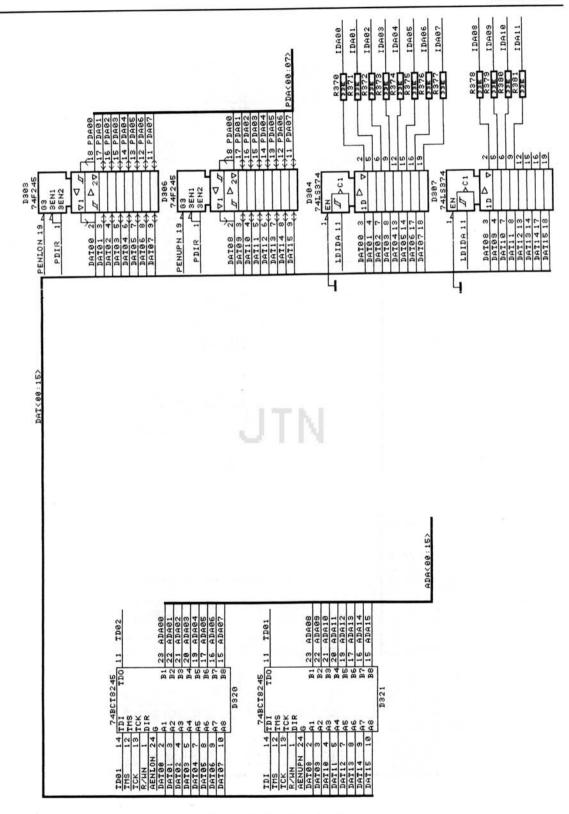

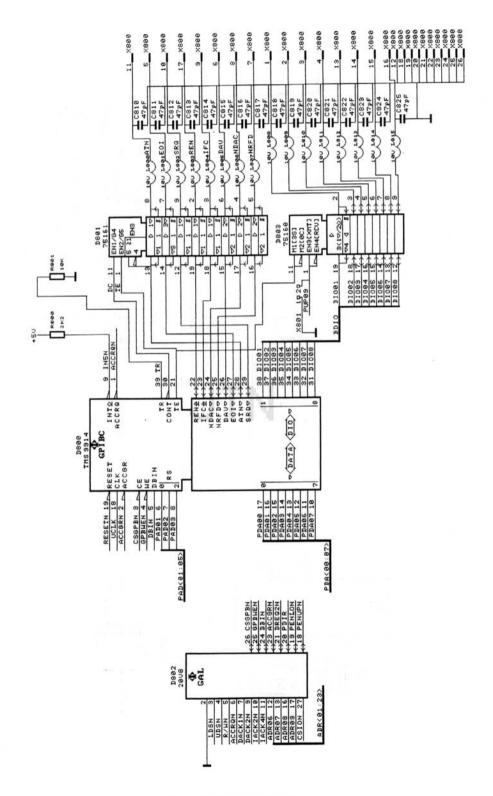

#### 3.7.3.5 Data buffers.

Refer to Fig. 3.20.

There are 2 data buffers (D303 and D306) to communicate with the peripherals and 4 buffers (D304, D307, D321 and D326) for communication with the analyzer part of the main board. D303 and D306 are both enabled by GAL D802. D303 controls the lower byte of the data bus, while D306 controls the upper byte.

Buffer D304 and D307 are directly connected per bit to an individual Input ASIC (D1 to D12). Also D320 and D321 are directly connected to ASIC's on the analyzer part. These buffers are also prepared to enable the usage of boundary scan tests.

#### 3.7.3.6 Address bus buffers.

Refer to Fig. 3.21.

The CPU address bus ADR01 - ADR11 is buffered for the analyzer part by boundary scan buffers D220 and D221.

The peripheral devices are controlled via ADR01 - ADR05 with buffer D203. The peripheral addresses are named PAD01 - PAD05. On the CPU address bus also D206 is connected, where this ASIC is mainly used for boundary scan and chip select purposes for the analyzer part.

Fig. 3.20. Data bus buffers.

Fig. 3.21. Address bus buffers.

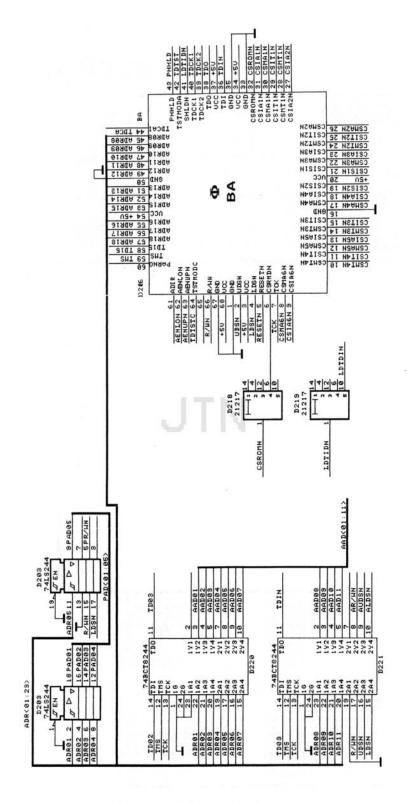

#### 3.7.3.7 Peripherals.

The following peripherals are used:

- Floppy Disc Controller (FDC)

Refer to Fig. 3.22.

- Centronics Parallel Controller Refer to Fig. 3.23.

- Multi Function Peripheral (MFP)

Refer to Fig. 3.24.

- The GPIB controller (IEEE) Refer to Fig. 3.25.

The peripherals are stand alone circuits which are connected to the CPU by buffers on the data bus (D303 and D306) and address bus (D203) and they communicate with the CPU via interrupts and DMA requests.

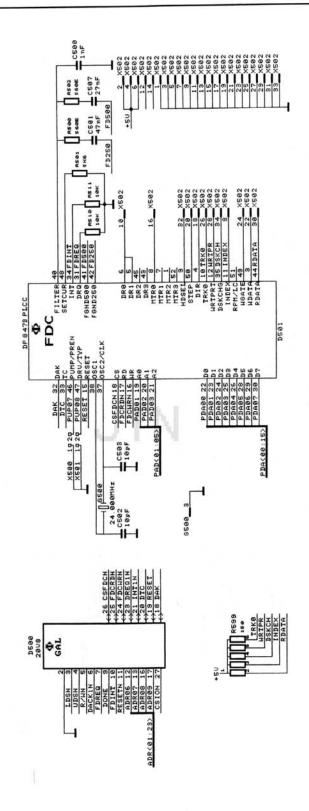

Floppy Disk Controller (FDC).

The *floppy disk controller* D501 is the DP8473 packed in a PLCC. This chip is directly controllable by the CPU via the peripheral data and address bus. The chip is selected by GAL D500 pin 26 with signal CSFDCN, while read and write actions are controlled via pins 24 (write) and 25 (read) of the GAL. The FDC asserts a DMA request (FDREQ) when I/O actions with the floppy are desired. This signal is sent to the GAL which in turn sends a DREQ1N (DMA request 1) to the CPU. If the DMA request of the FDC is accepted, the CPU returns a DMA-acknowledge (DACK1N) to the GAL, and via pin 18 of the GAL the signal DAK is asserted to the FDC. Now a bus transfer of data to or from the system memory can be accomplished. Pin 33 of the FDC is used to indicate the completion of the transfer per block (DTC = Data Transfer Complete).

All timing of the FDC is controlled by its internal timing mechanism, via an external oscillator

frequency of 24 MHz.

A Phase Locked Loop circuit (PLL) synchronises the incoming data on pin 44 (read data). Depending on the floppy density the appropriate PLL frequency is selected via filters R500 and C501 or R502 and C507.

All FDC signals from the floppy are directly (internally buffered) connected to the drive via connector X502.

Fig. 3.22. Floppy disc controller.

Fig. 3.23. Centronics parallel controller.

#### Centronics Parallel Controller.

IC D701 is the 68230 parallel interface and timer chip (PI/T).

The chip has 2 parallel ports (A and B). Port A is used as an 8 bit parallel output port. The 8 bits are buffered by D702 and D700 before they are sent to the printer connector X700.

Port B is partly used for boundary scan purposes (TDI, TDO and TMS), and partly as input to read the system board lay-out by the setting of the jumpers X703 and X704 (see also chapter 4.3.1 jumper settings).

Handshake is accomplished via signals H1 and H2 on pin 13 and pin 14.

GAL D703 selects with signal (CSPARN) on pin 25 the parallel controller, and with pin 26 (CSMFPN) the multi function peripheral (see next page).

The parallel controller has also a general purpose port C, which is used to guard the printer status (select, paper end and busy).

The communication with the CPU is based on interrupts (IN2N and IACK2N).

Every read and write action with the CPU is acknowledged by the parallel controller with pin 42 (DTACKN).

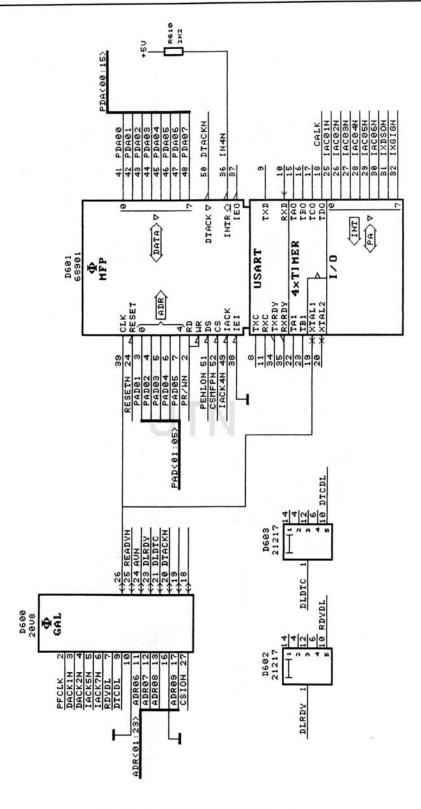

# Multi Function Peripheral (MFP).

The MFP IC D601 (68901) has an on-chip USART, 4 timers and an 8 bit general purpose I/O port. The USART and 3 timers are intended for future use, while the I/O port is mainly intended as an interrupt control port, connected to the analyzer ASIC's.

GAL D600 divides the 8 MHz peripheral clock (PFCLK) by 2 and its output pin 26 is directly connected to the clock and Xtal input of the MFP.

The MFP communicates via interrupt signals IN4N and IACK4N with the 68070, and also asserts a DTACK (data transfer acknowledge) at every read and write action.

Pin 18 of the MFP delivers the calibration clock during the calibration mode of the analyzer.

JTN

Fig. 3.24. Multi function peripheral.

Fig. 3.25. GPIB controller.

#### The GPIB Controller (IEEE).

The TMS 9914 (D800) is the general purpose interface bus chip for IEEE control.

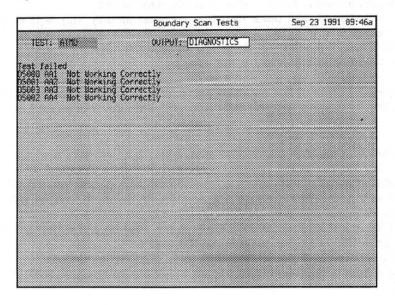

X800 can be connected to an external IEEE bus. The IEEE hardware is not implemented but can optionally be installed on the main-board.