# Logic Analyzers PM 3551 A / 10 / 30 / 50 / 70

# Operating manual

9499 500 12911 831013

A PUBLICATION OF THE SCIENTIFIC AND INDUSTRIAL EQUIPMENT DIVISION

© PHILIPS EXPORT B.V. - EINDHOVEN - THE NETHERLANDS - 1983

PRINTED IN THE NETHERLANDS

# TABLE OF CONTENTS

| Section | Description                                     | Page  |

|---------|-------------------------------------------------|-------|

| 1       | INTRODUCTION                                    | 1.4   |

| 1.1     | General information                             | 1.4   |

| 1.2     | Features                                        | 1.5   |

|         |                                                 |       |

| 2       | CHARACTERISTICS                                 | 2.1   |

| 2.1     | Logic State analyzer                            | 2.4   |

| 2.2     | Logic Timing analyzer                           |       |

| 2.3     | Operation                                       | 2.11  |

| 2.4     | Display                                         | 2.11  |

| 2.5     | Display modes                                   |       |

| 2.6     | Compare mode                                    |       |

| 2.7     | Power supply                                    |       |

| 2.8     | Environmental characteristics                   |       |

| 2.9     | Physical characteristics                        |       |

| 2.10    | Accessories and Options                         | 2.17  |

| •       |                                                 |       |

| 3       | GENERAL DIRECTIONS                              |       |

| 3.1     | Information and Warnings for the User           |       |

| 3.2     | Description of controls, connectors and display |       |

| 3.2.1   | Front panel                                     |       |

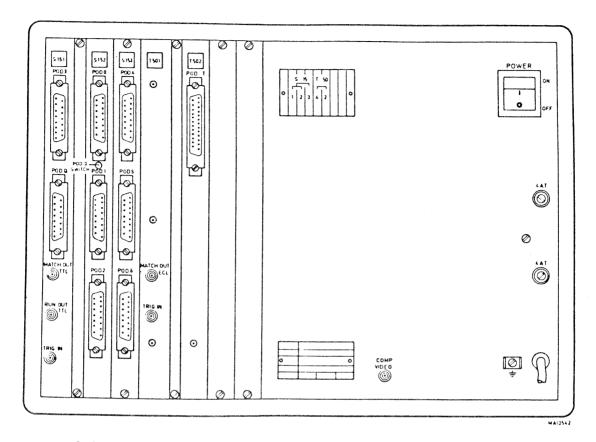

| 3.2.2   | Rear panel                                      | 3.9   |

| 1.      |                                                 |       |

| 4       | DESCRIPTION OF THE MENUS                        |       |

| 4.1     | Full menus                                      |       |

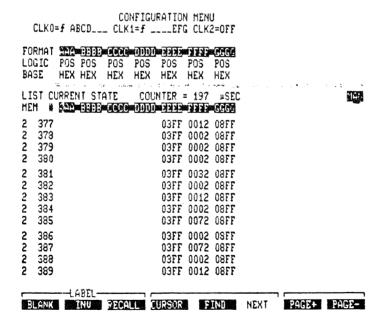

| 4.1.1   | Configuration menu                              |       |

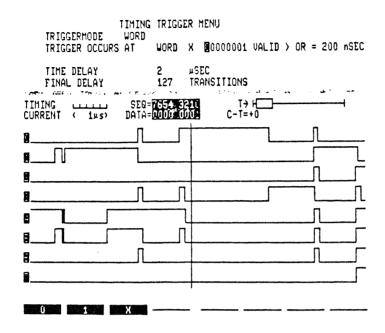

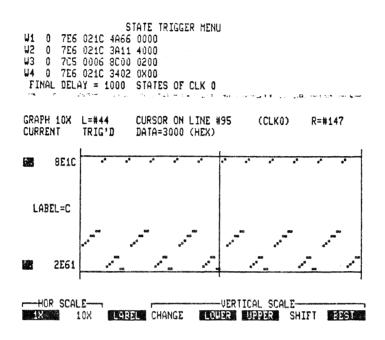

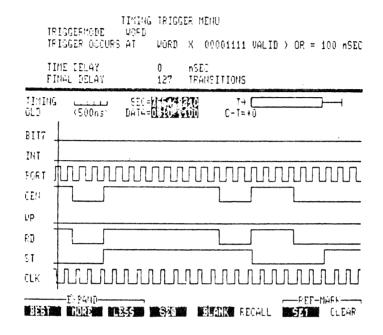

| 4.1.2   | Trigger menu                                    |       |

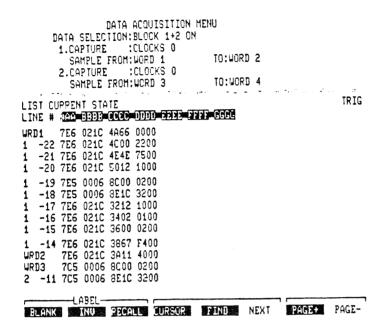

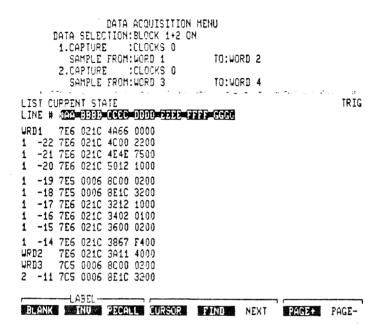

| 4.1.3   | Data menu                                       |       |

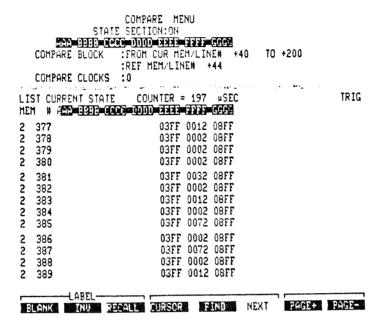

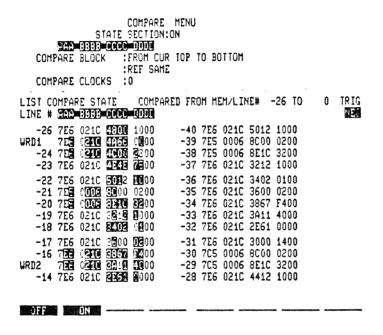

| 4.1.4   | Compare menu                                    |       |

| 4.1.5   | Options menu                                    |       |

| 4.2     | Condensed menus                                 | 4.32  |

| 5       | DECCRIPATION OF THE DAMA DIGREAM                | r 1   |

| 5.1     | DESCRIPTION OF THE DATA DISPLAYS                |       |

| 5.1.1   | List                                            |       |

| 5.1.2   | Selective data                                  |       |

| 5.2     | Craph                                           |       |

| 5.3     | Graph                                           |       |

| 5.3.1   | Timing                                          |       |

| 5.4     | Timing compare                                  |       |

| 3.4     | bythe mode                                      | 2.10  |

| 6       | CONNECTION                                      | 6 1   |

| 6.1     | Input                                           |       |

| 6.2     | What else to connect?                           |       |

| 0.2     | what else to connect:                           | 0.5   |

| 7       | USER MESSAGE LIST                               | 7 1   |

|         |                                                 | , • I |

| 8       | OPERATION                                       | 8.1   |

| 8.1     | General                                         |       |

| 18.2    | Triggering                                      |       |

| 8.3     | Selective data acquisition                      |       |

| 8.4     | Compare                                         |       |

|         |                                                 | ~ · · |

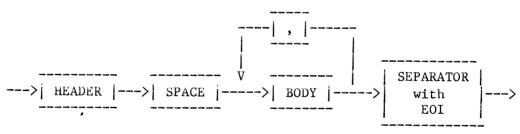

->

# TABLE OF CONTENTS (cont'd)

| Section       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 9             | INTERFACE AND OPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

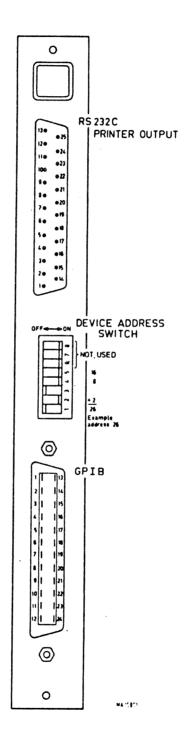

| 9.1           | Printer Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _    |

| 9.2           | Disassemblers General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| 9.2.1         | Disassemblers Accesories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| 9.2.2         | Non-volatile memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9.7  |

| 9.3           | Disassembler connection and display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9.10 |

| 9.3.1         | A Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| 9.3.2         | M Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| 9.3.3         | N Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| 9.3.4         | R Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| 9.3.5         | Z Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| <b>7.3.</b> 3 | 2 Tackage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

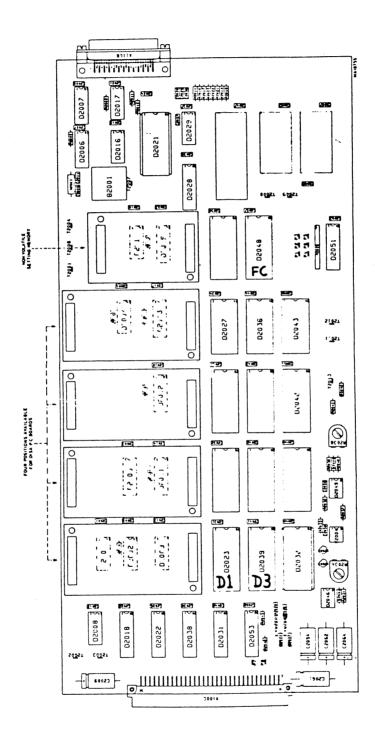

| 10            | INSTALLATION INSTRUCTIONS FOR OPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10.1 |

| 10.1          | Unit identifier switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10.3 |

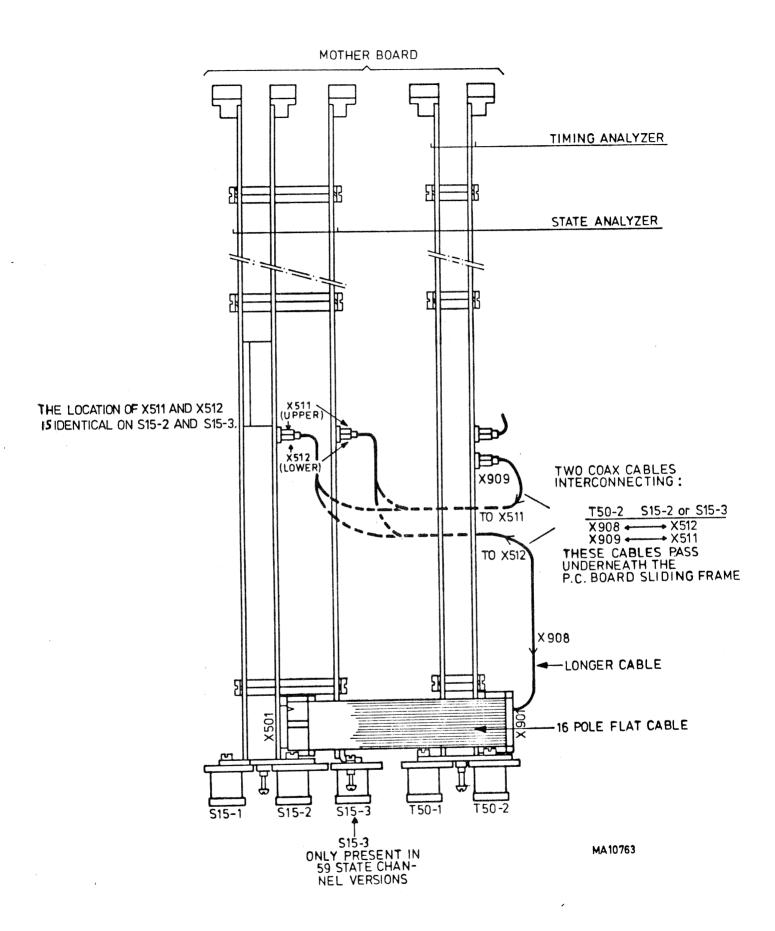

| 10.2          | Additional 24-channel state analyzer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10.4 |

| 10.3          | 8-channel 50 MHz timing analyzer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

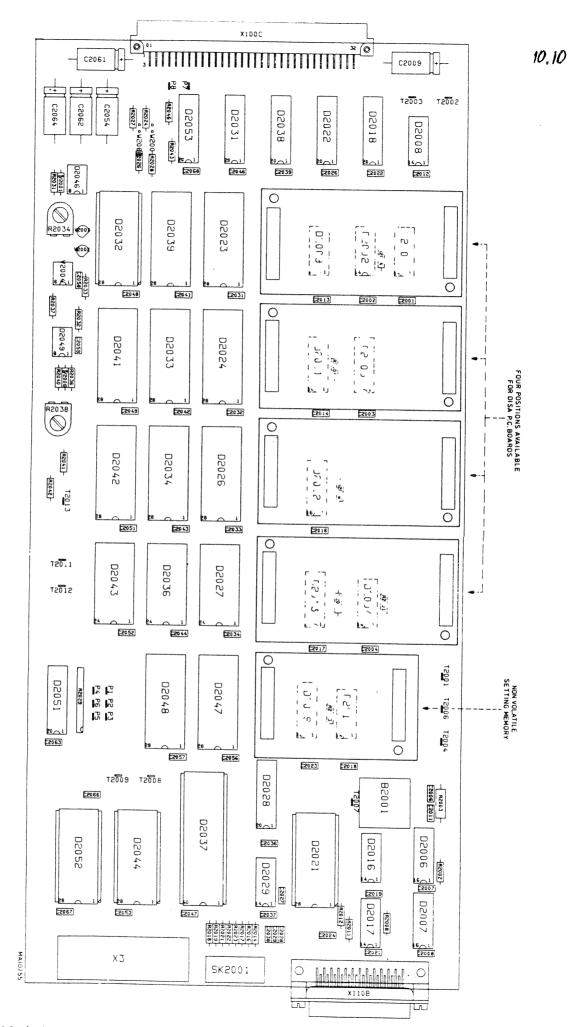

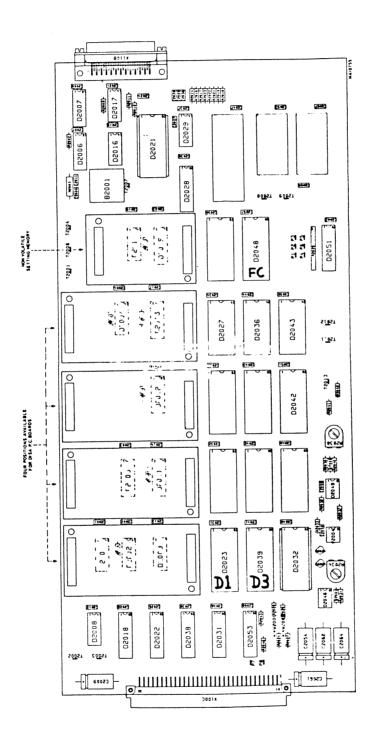

| 10.4          | Option board, disa's and non-volatile memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|               | , and a second of the second o |      |

| 11            | IEEE-488 GPIB INTERFACE OPTION (PM 8851/40)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11.1 |

| 12            | RS 232-C CONTROL INTERFACE OPTION (PM 8851/20)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12.1 |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 13            | PROBLEM REPORTS AND CHANGE REQUESTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13.1 |

INTRODUCTION

#### 1. INTRODUCTION

# GENERAL INFORMATION

The Philips PM3551A Logic Analyzer family comprises 4 main types: PM3551A/10, PM3551A/30, PM3551A/50 and PM3551A/70, each type containing features suitable for a variety of application needs.

This manual contains information to operate the whole range of models. The PM3551A/30 and PM3551A/70 are compact instruments whose easy-to-operate design offers the user a very comprehensive selection of Time, Data and Graph analysis features. The extensive measurement capabilities will enable the user to test and troubleshoot a wide range of digital systems, with the additional plus factor that theinstruments are extremely well suited for use in a teaching environment.

The PM3551A/70 is capable of recording a maximum of 59 state channels and 8 $50 \mathrm{MHz}$  timing channels while the PM3551A/30 although identical in design and operation is capable of measuring a maximum of 35 state channels and 8 50MHz timing channels.

The PM3551A/10 and PM3551A/50 have the same features as the above mentioned PM3551A/30 and PM3551A/70 models with the exception of the "50MHz Timing Analyzer" mode.

The operator control panel is divided into several functional areas which guide and help the user to set up the most effective test procedure.

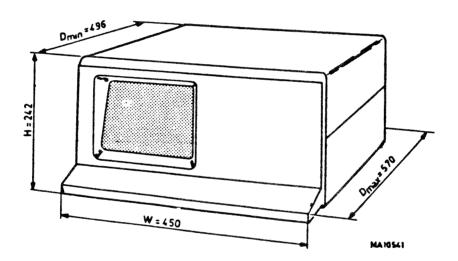

Fig.1.1. Logic Analyzer PM3551A

## 1.2. FEATURES

A functionally organized keyboard/softkey structure in combination with an interactive menu-display serve the user in setting up and entering parameters for triggering, capturing, comparing and counting the activities of the system under test.

The extensive triggering capability of the 7 sequential trigger-words, that can be combined with clock and trigger-qualifiers, permits capturing data from complex system activities or from deep branched or nested loops. Each trigger-word has the same width as the number of input channels of the various models.

The sequence of the different trigger-words used can be defined by the use of an IF, THEN, ELSE algorithm, with the possiblity of placing a certain amount of delay between the statements.

In this mode triggering can be selected as True or False.

A notable feature of this mode is that the selected trigger sequence can be specified as true or alternatively as not true. This latter mode is called "Trigger on Sequence Break" mode and provides the capability of triggering when a defined repetitive pattern (eg. a loop or a polling sequence) is broken or not executed in the specified order.

The moment of capturing data can be delayed by states and/or trigger occurrences and/or time.

The Logic Analyzer can also be used for making time measurements. A readout of the elapsed time between two points in a programm can be obtained.

Special features of note here are the COMBI and the SYNC modes. The COMBI mode allows the state section to be triggered by the timing section or vice-versa, while in the SYNC mode the displays of a number of timing channels are cross-referenced with state sampling. This enables analysis of critical state/time relationships.

Data to be captured is clocked into the analyzer on selected clock edges of one of the three selectable clock sources. For each clock used, there are up to four qualifiers available.

In the COMPARE mode, a comparison can be made between captured data and stored data in the formats: List or Timing.

The instrument automatically stores the current mode- and function instrument-setting, when the mains voltage supply is switched off.

After switching on, the instrument comes up in the initial default mode- and function setting.

All analyzer models can be equipped with the option (non-volatile memory) to store up to 4 additional settings. Here each setting is stored and retrieved under a label.

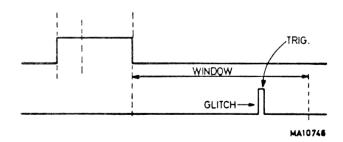

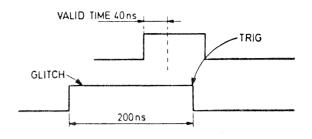

In the TIMING mode, glitches of a duration of as little as 5 nanoseconds can be captured from the data-stream.

The PM 3551A can be equipped with a 4 channel 300MHz timing option, independently of the presence of the 8 channel 50 MHZ section. This allows high precision timing measurements.

Other options are the options board with standard RS232C printer output. This board can be equiped with an GPIB control interface, or a RS232C control interface, both providing full remote control of the instrument.

The options board is also a prerequisite for installation of disassembly-packages, and the non-volatile setting memory. The disassembly-packages allow the user to view captured data in the mnemonic language of the most currently available 8 and 16-bit microprocessors.

Data is entered into the analyzer via 8-channel pods, each provided with its own threshold adjustment. A variety of convenient Pod-attachments are available for connecting the system under test to the analyzer.

A comprehensive built-in diagnostic program can be used as an aid to test the various functions of the analyzer and to assist in fault-finding. CHARACTERISTICS

#### 2. CHARACTERISTICS

The instrument has been designed and tested according to IEC Publication 348 for Class I instruments and has been supplied in a safe condition. The present Operating Manual contains information and warnings which should be followed by the purchaser to ensure safe operation and to maintain the instrument in a safe condition.

Properties expressed in numerical values with stated tolerances are guaranteed for ambient temperatures of +5 deg.C  $\dots$  +40 deg.C unless stated otherwise. Numerical values without tolerances are typical and represent the characteristics of an average instrument. This specification is valid after the instrument has warmed up for 15 minutes.

OPERATION MODES:

- Logic State Analyzer only

- Logic Timing Analyzer only

- Combi Mode where the LSA can enable the triggering of the LTA or vice-versa.

- SYNC Mode where timing analyzer data is cross-referenced with the state analyzer data.

TYPES:

|    |    | Type  | -numbers    | PM3551A | ./10 | PM3551A/30 | PM3551A/50 | PM3551A/70 |

|----|----|-------|-------------|---------|------|------------|------------|------------|

| No | of | State | Channels    |         | 35   | 35         | 59         | 59         |

| No | of | 50MHz | Timing Char | nels    |      | 8          | -          | 8          |

MA 10030

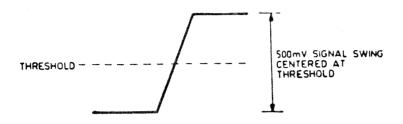

Fig. 2.1 Minimal signal swing

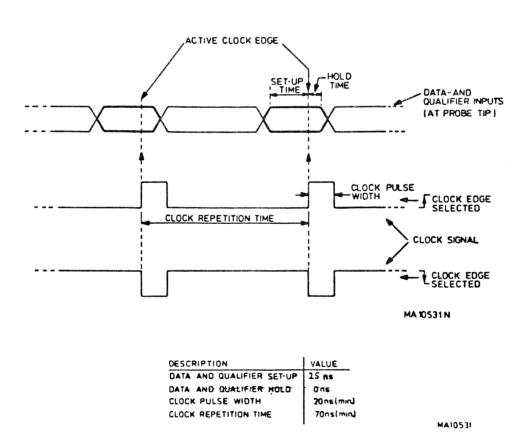

Fig. 2.2 Definition of terms and times

#### 2.1 LOGIC STATE ANALYZER

Data Input : PM3551A/10: 35 channels max. via 5 Pods PM 8821

PM3551A/30: 35 channels max. 27 via 4 Pods PM 8821 + 8 via 1 Pod PM8825

PM3551A/50: 59 channels max. via 8 Pods PM 8821

PM3551A/70: 59 channels max. 51 via 7 Pods PM8821 + 8 via 1 Pod PM8825

Pod Type : PM8821 and PM8825 8-ch. input probe Pods

to be connected at the rear of the

instrument.

Following values are typical values and specified at the probe tip(s)

Impedance : 4 MOhm//6 pf

Max. input voltage : -50 V to +50 V

Threshold : Selectable per Pod.

Fixed TTL, ECL or VARiable between -3V and +12 V

in 100mV steps.

Max. sensitivity : 500 mV pp signal swing, centered on the

threshold voltage (see Fig. 2.1).

Set-up and hold

times

: Data set-up time minimum 25ns Data hold time minimum Ons

Both related to the active clock edge at

the probe tip (see Fig. 2.2).

Data aquisition : Data collected is selectable from:

a. states i.e. all combinations at inputs

are clocked in.

b. occurrances i.e. only certain types

of words are acquired.

c. combination of both.

Clock

Source : External (synchronous) clocking.

Number of clocks : Three separate clocks can be acquired via

3 leads of a Pod PM8821.

Threshold : Same specification as data input (see also

Fig. 2.1).

Impedance and

max. input voltage

: Same specification as data input

time

Clock repetition : Min. 70ns (see Fig. 2.2).

Clockpulse width

: Min. 20ns (see Fig. 2.2).

Sampling

: Selectable on positive or negative clock

edge.

# Clock qualifiers

Number

: 2...4 clock qualifiers (input via a Pod PM8821)

Two clock qualifiers are fixed, the other two are interchangeable with two data

channels.

Threshold

: Same specification as data input (see also

Fig. 2.1).

Impedance and

max. input voltage

: Same specification as data input

Sampling

: At clock edge and at selected qualifier

level. True and False combinations

are possible (see Fig. 2.2).

Selection

: "1" for a high level "0" for a low level

"X" for don't care (qualifier not in use).

Set-up and hold

times

: Data set-up time minimum 25ns Data hold time minimum Ons

Both related to the active clock edge at

the probe tip (see Fig. 2.2).

# Memory

Format

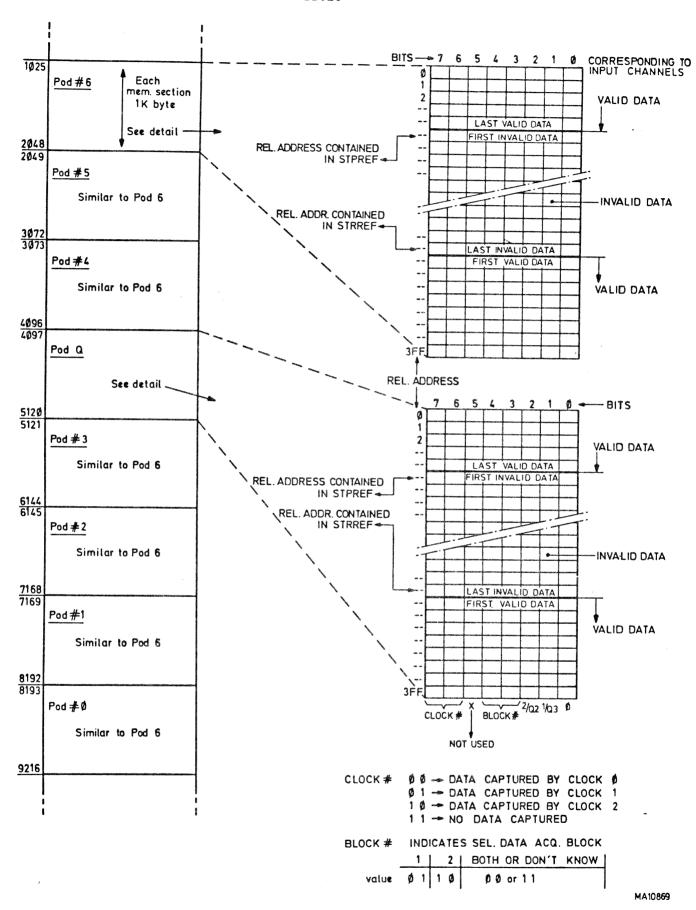

: The memory depth is 1K (=1023) bits per channel.

A second memory of the same size is available

as a reference memory for comparison

#### Triggering

Source

: 1) Internal, 2) Manual or 3) External (External socket TRIG IN is also input

for trigger qualifier)

1) Internal

- : Triggering on up to 7 words, each delayed by a delay counter, can be selected for:

- . Parallel and Quasi parallel triggering

- . Sequential triggering (ARM word(s) enable the TRIG word)

- . Immediate Sequential Triggering. Word N must be followed immediately by word N+1.

For all trigger modes, all combinations can be made with up to 7 words, clocks and delays.

Trigger words can be selected for "true" or "false" triggering.

The number of triggers can be preset and counted (see: Delay and Counter).

2) Manual

: Operator controlled STOP button.

3) External i.e. external trigger trig. qualifier

: Via input socket TRIG IN and PM8800 or PM 8810 probes. This input acts as an enable for the internal trigger logic and is selectable as edge or level active.

The external input offers the following possibilities:

- . When the internal trigger word is set as all don't cares, this input acts as an external trigger.

- . When the internal trigger word is defined this input acts as a trigger qualifier.

- . Connection for PM8810 Logic Trigger Probe

Following values are typical values and apply only when the specified probe is used.

Input Impedance

: 5 MOhm // 15 pf

Max. Input Voltage : + 50 V

Threshold

: Fixed TTL

Sensitivity

: 500 mV<sub>pp</sub> signal swing (see Fig. 2.1)

Set-up and hold

times when PM8800

is used

: Signal set-up time minimum 30ns Signal hold time minimum Ons

Both related to the active clock edge at

the probe tip (see Fig. 2.2).

(use the 'delayed' function in the trigger menu)

Set-up and hold times when PM8810

is used

: Signal set-up time minimum 50ns Signal hold time minimum 5ns

Both related to the active clock edge at

the probe tip.

(use the 'not-delayed' function in the

trigger menu)

Delay

: In the trigger menu, delay can be specified

in the range of 0 to 64k steps

as states of clock(s)in occurrences of word(s)

- in time

Outputs

: -MATCH OUT. Is activated by the MATCH OUTPUT ON WORDS:-statement in the trigger

sequence list.

The output is TTL high when the trigger word occurs, and remains high until the

next trigger word occurs.

The delay between input probe tip (PM 8821) and the Match out connector amounts to: 3 state clock cycles +50 +/-15 nS.

The pulse length is always more than 60 nS.

-RUN OUT. The output is TTL high during

data acquisition.

The delay between internal start and stop,

and the output is 25 + /-15 nS.

Output specification:

-TTL compatible

-Source current 3 mA at Voh= 2,4 V. -Sink current 3 mA at Vol= 0,5 V.

-Short-circuit proof.

-Max. ext. voltage + or -25 V.

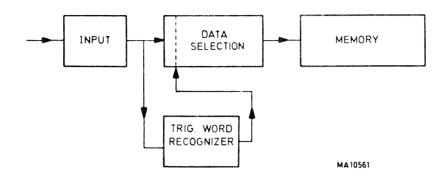

# Selective data acquisition

Selection

: Up to two different blocks of selective data acquisition can be selected.

Block limits

: Start on a certain word or on START.

End on a certain word, word+trigger delay,

or END.

Selected data

: Samples on specified clock(s).

-A specific word and samples on specified

clock(s).

-One specific word.

-A specific word followed by a number (max. 255) samples on specified clocks. This can be limited by a max. repeat of 512

Counter

: In Selective data menu, between specified start and finish, a counter can count:

-Samples with specific clock(s)

-Specific words

-Time

# 2.2 LOGIC TIMING ANALYZER

Data Input : 8 channels via 1 Pod

Pod Type : PM8825, to be connected at the rear of the

instrument.

Following values are typical values and specified at the probe tip(s).

Impedance : 1 MOhm // 5 pf

Max. Input voltage : -50V to +50V

Threshold : TTL, ECL or VARiable between -3 and +12V

in 100mV steps.

Max. sensitivity : + 200 mV. with respect to threshold level.

Maximum non-detect-

able pulse width : 24 ns (=set up, + hold time + sample interval)

Channel to channel : <3 ns

skew

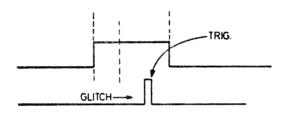

Glitch detection : Selectable over all 8 channels.

> Glitches from 20ns sample period down to 5ns, selectable by user.

Clock

Source : Internal

Fixed 20 ns (i.e. 50 MHz), transitional clocking system (refer to chapter 8).

Memory

Depth

: 1/4 K bits per channel. (recording up to 256x10<sup>6</sup> samples)

Triggering

Source : 1) Internal, 2) Manual, 3) External and

4) Glitch

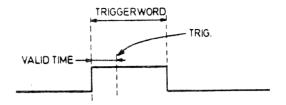

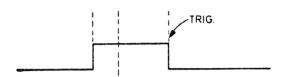

1) Internal : 3 modes: Word

Word + Glitch

Glitch after window

Triggering selectable on leading or

trailing edge of word match.

Timing and State can be combined in

COMBI mode and SYNC mode.

2) Manual : Operator controlled STOP. 3) External

: Via input socket TRIG IN (T15-1) and PM8800 probe. This input is edge active. Values apply only when the belonging PM8800 probe is

used.

This input can be used as input for a trigger-

or glitch qualifier signal.

Trigger filter

: Selectable between 20ns--300ns,

in 20ns steps.

Input impedance

: 5 MOhm // 15 pf

Max. input voltage : + 50 V

Threshold level

: Same voltage at PM 8800 probe tip as at the

input of the PM 8825 Pod.

Sensitivity

: 300 mVp-p with respect to threshold level.

Min. pulse width

: 5 ns.

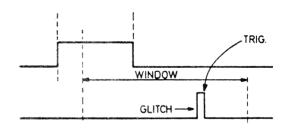

4) Glitchtriggering: Triggering on glitches on one selected channel with a selected glitch width of minimum 5 ns. up to a maximum of N sample intervals where N is selectable between 1 and 15. One sample interval is 20 ns.

Glitch window

: Defining a window by an arming word (start)

plus a delay (finish) within which the

analyzer is looking for glitches.

Glitch-qualifier

Trigger-qualifier

: Via input socket TRIG IN and PM8800 probe with the same characteristics as under

'External'.

Used as a glitch-qualifier, an extra trigger condition is added to the glitch-triggering. Used as a trigger-qualifier it enables the

selected timing triggerword to be extended with

one bit.

Delay: 1) Time delay and 2) Final delay

1) Time delay

: Max.  $20 \times 2^{20}$  nsec. = 20971 usec.

via a 20 bit counter which counts in steps

of 20 nsec.

2) Final delay

: Max. 255 transitions

Output

: MATCH OUT: ECL level,

High, when the selected trigger word is true

until the next trigger word appears. (output via BNC connector at rear side)

Input

: TRIG IN:

(input via BNC connector at rear side).

## 2.3 OPERATION

Key-board keys

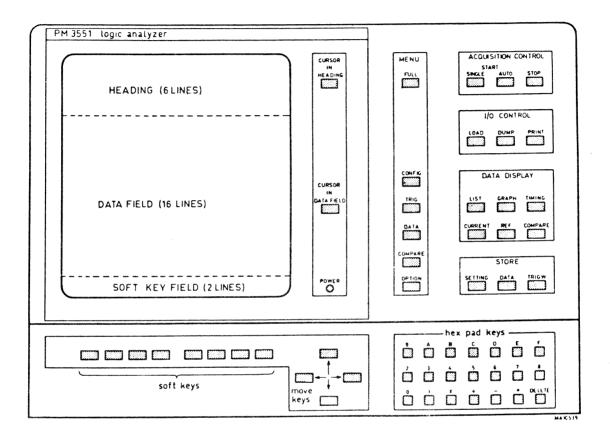

Operation is by key actions combined with various data or menu displays. The keys are divided into two key fields, see also the front panel lay-out, Fig.3.2.

Front panel keys : Allow user direct access to the analyzer display modes and control functions.

display modes and control lunctions.

: Allow the user to enter the required parameters within a display mode. This keyboard is based on a combination of hard-keys (for cursor control and HEX value entry) and soft-keys (when entry is not a

HEX character).

# 2.4 DISPLAY

The display is a green phosphor 9 inch video display. This video display can show a maximum of 24 text lines when the instrument is in a full menu mode. When in data display mode the display is divided into three fields (see also front panel layout, Fig.3.2).

Heading : The top 6 lines of the display which contain a condensed menu display.

Data field : The centre 16 lines of the display.

This area contains the data display.

Softkey function : The bottom 2 lines of the display which display the functions of the softkeys

located under the display.

#### EXTERNAL DISPLAY

: Via BNC output connector COMP VIDEO at the rear side of the instrument.

- Display scan : Non-interlaced

- Number of display lines : Total 312, visible 256

- Cable matching impedance : 75 Ohm

- Polarity : High level is bright : 20%...40% of total

- Line frequency : 15600 Hz - Frame frequency : 50 Hz - Max video bandwidth : 10,7 MHz

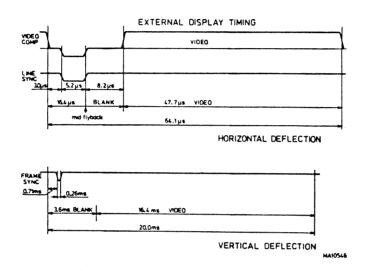

- External display timing : See figure 2.3.

Fig. 2.3 External display timing

#### 2.5 DISPLAY MODES

Data display

- : State list display; binary, octal, decimal, hexadecimal, ASCII or combinations of these. Inverted display by groups or by individual channels is possible.

- : Graphic display; data magnitude is plotted against sample sequence.

- : Timing display; 8 channel format, vertical expansion by channel delete, horizontal scale continuously controllable.

Menu display

- : For specification of parameter set—ups the following menus can be displayed:

- Configuration menu

- Trigger menu (State or Timing)

- Data menu

- Compare menu

- Option menu

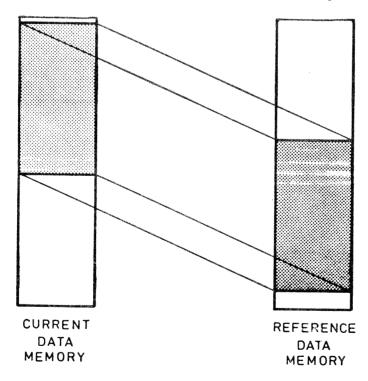

# 2.6 COMPARE MODE

Memory

: A reference memory is available to store the contents of the acquisition memories of both state and timing. This memory can also be loaded via the optional interface.

Store

: With the store function, data contained in the acquisition memory is copied into the reference memory.

Modes

: Full compare:

The two entire memories are compared.

Compare Mask:

Channels over which the compare takes place and the limits of the compare with respect to the trigger point are defined by the user.

Offset:

Shift of stored data (masked) with respect to current data.

Skew:

Timing only

This allows deviation of an edge in the current data with respect to stored data.

Search:

Stops continuous compare process when an inequality is found, or counts equalities or inequalities.

# 2.7 POWER SUPPLY

Safety Class

: I IEC-348, ECMA-57

Nominal mainsvoltage ranges : 110...127 Vac + 10% or

Mains fuses 4A delayed (2x), both

220...240 Vac + 10%

mains-voltage

ranges

Nominal frequency

range

: 50...60 Hz + 10%

Power consumption

: 130 VA : 250 VA : 180 VA

PM 3551A/10 PM 3551A/30 PM 3551A/50

: 280 VA

PM 3551A/70

#### 2.8 ENVIRONMENTAL CHARACTERISTICS

The characteristics are valid only if the instrument is checked in accordance with the official checking procedure. Details of these procedures and failure criteria are supplied on request by the PHILIPS organization in you country, or by N.V. PHILIPS' GLOEILAMPENFABRIEKEN, TEST AND MEASURING DEPARTMENT, EINDHOVEN, THE NETHERLANDS.

## -CLIMATIC CONDITIONS

### Ambient temperature

Rated range of use + 5 ...+ 40 Deg.C

0 ...+ 45 Deg.C Limit range of operation

-40 ...+ 70 Deg.C Limit range for storage and transport

# Relative humidity

Rated range of use 20% ... 80% Non condensing

5% ... 95% Limit range for storage and transport

#### Altitude

Rated range of use up to 5000 m.

Limit range for up to 15000 m. storage and transport

#### Mains Interruption

10 ms (nominal No influence on mains supply) settings and data

storage.

#### -MECHANICAL CONDITIONS

Vibration

Rated range of use

Negligible value

Limit range for

storage and transport

0.28 mm(p-p) max. 20 m/s

Frequency range

10 ... 150 Hz

Bump

Rated range of use

$10 \text{ m/s}^2$

6 ms

Limit range for

$100 \text{ m/s}^2$

1000X, 6 ms in each

storage and transport

of 3 directions

ELECTROMAGNETIC COMPATIBILITY (EMC)

Electromagnetic Interference (EMI)

Conducted interference

level B

VDE 0871

Radiated interference

level B

10 kHz ... 30 MHz

VDE 0871

Electromagnetic susceptibility (EMS)

Conducted susceptibility

Transients on mains

connections (ingoing)

Assymetrical only

Fast low energy pulses

Pulse height

1500 V max.

No damage to occur

Rise time

35 ns. max.

Pulse width

Source impedance

100 ns. approx. 150 Ohm max.

# 2.9 PHYSICAL CHARACTERISTICS

# Dimensions

| Width             | 450 mm |

|-------------------|--------|

| Heigth incl. feet | 242 mm |

| Heigth excl. feet | 227 mm |

| Depth max.        | 570 mm |

| Depth min.        | 496 mm |

# Weigth

Net, without 17 kg(approx.) accessories and options

Fig. 2.4 Dimensional drawing

# 2.10 ACCESSORIES AND OPTIONS

# -Accessories included in delivery:

```

1 Operating manual

5 8-channel pods (with PM 3551A/10) PM 8821

4 8-channel pods (with PM 3551A/30) PM 8821

8 8-channel pods (with PM 3551A/50) PM 8821

7 8-channel pods (with PM 3551A/70) PM 8821

1 8-channel timing pod (with PM 3551A/30 & /70) PM 8825

```

# -Instrument "upgrading" options (These options are field-installable):

```

PM 8850/00 DISA A (Z80, 8085, 68000)

PM 8850/10 DISA N (Intel)

PM 8850/20 DISA M (Motorola)

PM 8850/30 DISA Z (Zilog)

PM 8850/40 DISA R (Rockwell/RCA/NS)

PM 8850/81 Non-volatile memory for storage of 4 user-defined instrument settings for PM 8851/00.

PM 8850/82 Same as PM 8850/81 but for PM 8851/20 and /40.

```

The above PM 8850/xx options can be installed on the Options board PM 8851/00/20 or /40.

| PM 8851/00  | Options board with printer output for PM 3551 and 3551A. |

|-------------|----------------------------------------------------------|

| PM 8851/20  | Options board with printer output + RS 232C control      |

|             | interface for PM 3551 and PM 3551A.                      |

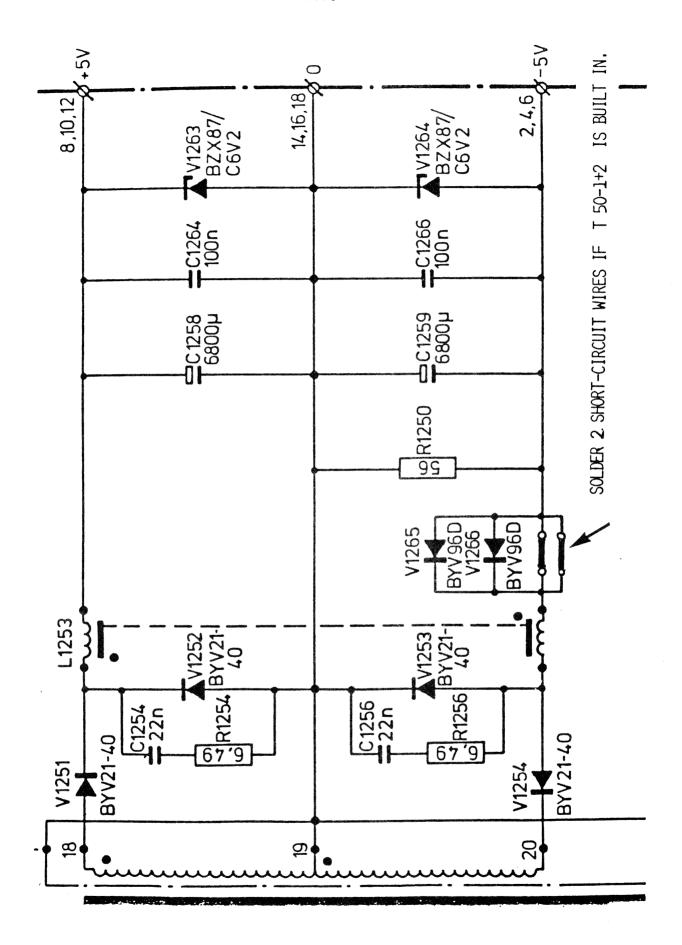

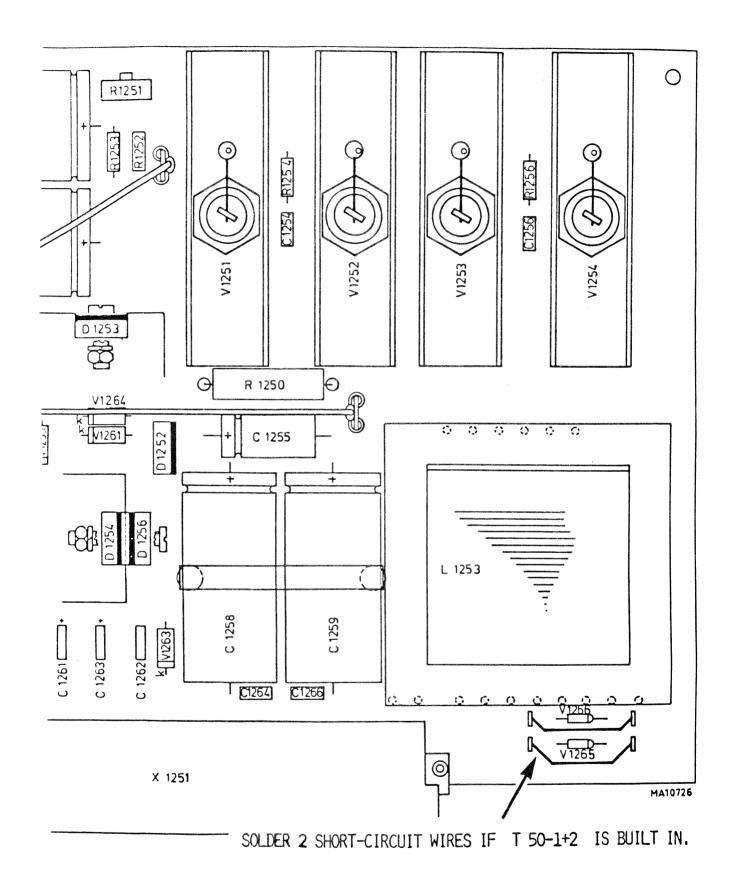

| PM 8851/30  | 8 channel 50 MHz timing analyzer (T50-1,2) for PM 3551.  |

| PM 8851/40  | Options board with printer output + IEEE 488 (IEC 625)   |

|             | control interface for PM 3551 and PM 3551A.              |

| PM 8851/50  | 24 channel state analyzer option (S15-3) for PM 3551.    |

| PM 8851/80  | 4 channel timing analyzer 300 MHz option for PM 3551.    |

| PM 8852/30  | 8 channel 50 MHz timing analyzer (T50-1,2) for PM 3551A. |

| PM 8852/50  | 24 channel state analyzer option (S15-3) for PM 3551A.   |

| PM 8852/80  |                                                          |

| 211 0032/00 | 4 channel timing analyzer 300 MHz option for PM 3551A.   |

The printer output is always RS232C.

# -Optional accessories:

| PM 8800    | External trigger probe (set of four probes)           |

|------------|-------------------------------------------------------|

| PM 8810    | Logic trigger probe                                   |

| PM 8811    | Serial data pod                                       |

| PM 8817/40 | Personality adaptor for 40-pin micro processors       |

| PM 8817/64 | Personality adaptor for 64-pin micro processors       |

|            | The wiring interface box PM 8816 of the PM 8817/40/64 |

|            | personality adaptors must be wired by the user.       |

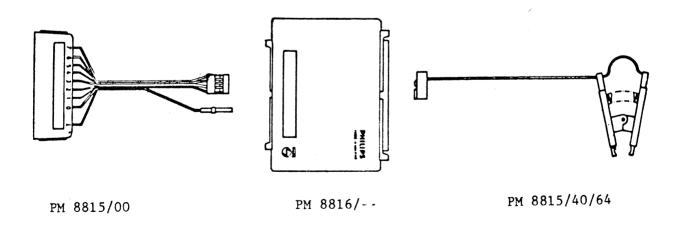

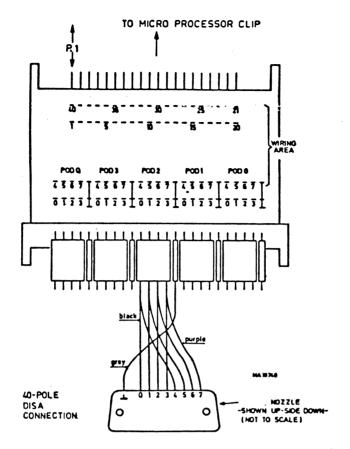

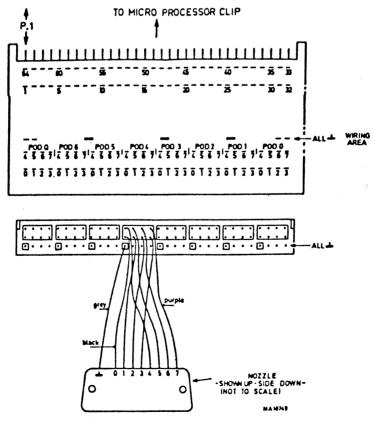

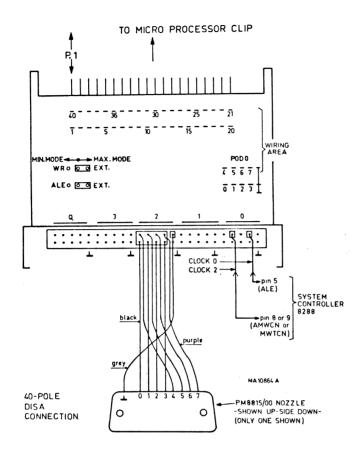

A PM 8817 consists of a PM 8815 Pod nozzle, a wiring interface box PM 8816, and a micro processor test clip with ribbon cable PM 8815/40/64.

The following personality adaptors are specific for the disassembler of the indicated micro processors.

| Adaptor    | Microprocessor |

|------------|----------------|

| PM 8817/10 | 6800/02/08     |

| PM 8817/12 | NSC800         |

| PM 8817/19 | 68000          |

| PM 8817/20 | 8085           |

| PM 8817/21 | 8048           |

| PM 8817/22 | Z80            |

| PM 8817/23 | Z8002          |

| PM 8817/24 | R6502/12       |

| PM 8817/26 | 6809/E         |

| PM 8817/27 | 8086/8088      |

| PM 8817/28 | 8080           |

# Parts of accessories:

| PM 8815/00 | Set of 5 Pod nozzles for personality adaptor.                             |

|------------|---------------------------------------------------------------------------|

| PM 8815/40 | 40-pin clip with ribbon cable.                                            |

| PM 8815/64 | 64-pin clip with ribbon cable.                                            |

| PM 8816/40 | Wiring interface box for 40-pin micro processors                          |

| PM 8816/64 | Wiring interface box for 64-pin micro processors                          |

| •          | Boxes PM 8816/40/64 must be wired by the user.                            |

| PM 8816/   | Wiring interface box (pre-wired) for commonly used                        |

|            | micro processors. They are available in the same versions as the PM 8817. |

| PM 8819/00 | Extension kit for PM 8821 (leads, clips and nozzle)                       |

| PM 8819/10 | 54 coloured leads for PM 8821 (length 26 cm)                              |

| PM 8819/20 | 35 measuring clips                                                        |

| PM 8819/30 | 50 mini dualclips                                                         |

| •          |                                                                           |

| PM 8819/40 | 54 coloured leads for PM 8825 (length 12 cm)                              |

Note: For more information refer to the chapter 9.

GENERAL DIRECTIONS

# 3.0 GENERAL DIRECTIONS

# 3.1 WARNINGS AND INFORMATION FOR THE USER

- It is recommended that this section is read completely before switching on the instrument.

- This instrument has been designed and tested in accordance with IEC Publication 348, Class 1, Safety Requirements for Electronic Measuring Instruments and has been supplied in safe condition. This Manual contains information and warnings, all of which must be considered to ensure safe and reliable operation of the instrument.

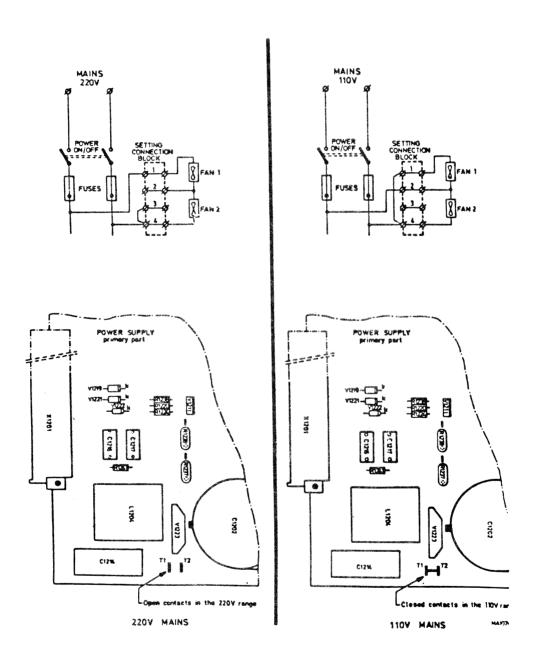

Fig. 3.1 Connecting for 220 V or 110 V range mains voltage.

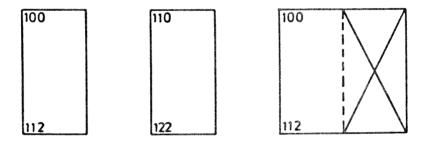

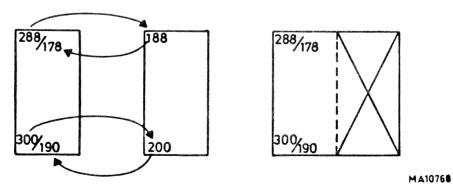

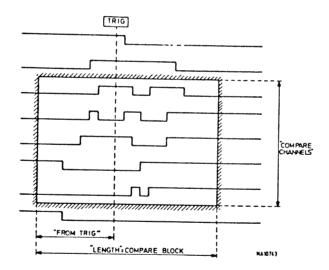

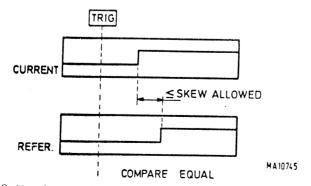

#### Mains adaption